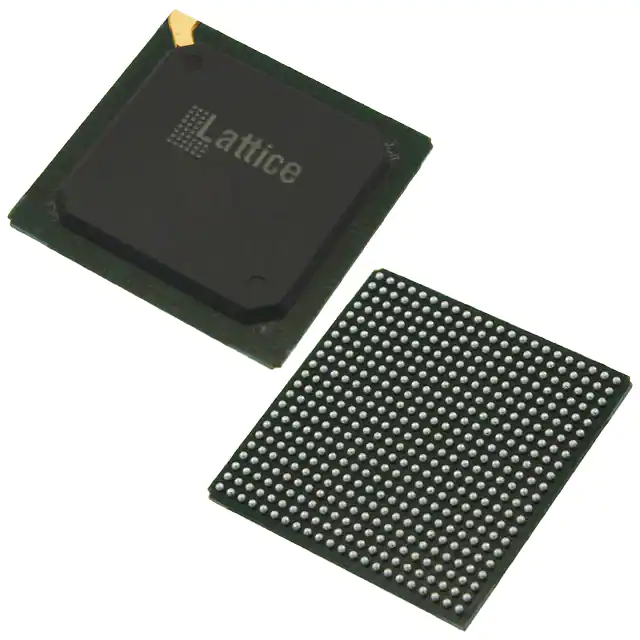

ispXPLD 5000MX系列代表了一类新的设备,称为扩展可编程逻辑设备(XPLD)。这些设备通过提供灵活的存储能力,扩展了莱迪思流行的SuperWIDE ispMACH 5000架构的功能。该系列支持单端口或双端口SRAM、FIFO和三元CAM操作。还包括了额外的逻辑,以允许算术函数的有效实现。此外,sysCLOCK PLL和sysIO接口为设计者的系统级需求提供支持。

这些设备为设计人员提供了方便的单芯片解决方案,可在启动时提供逻辑可用性、设计安全性和极强的可重新配置性。先进工艺技术的使用提供了业界领先的性能,组合传播延迟低至4.0ns,2.8ns时钟输出延迟,2.2ns设置时间,工作频率高达300MHz。这种性能与低静态和动态功耗相结合。ispXPLD 5000MX体系结构提供了可预测的确定性时序。

这些设备的3.3、2.5和1.8V版本的可用性以及sysIO接口的灵活性有助于用户应对当今混合电压设计的挑战。当I/O组配置为3.3V操作时,输入可安全驱动至5.5V,使该系列耐受5V电压。边界扫描可测试性进一步简化了与当今复杂系统的集成。各种密度和包装选项增加了适合特定应用的可能性。表1显示了ispXPLD 5000MX家族的成员。

特色

■ 灵活的多功能块(MFB)架构

•超宽™ 逻辑(最多136个输入)

•运算能力

•单端口或双端口SRAM

•FIFO

•三元CAM

■ 系统时钟™ PLL定时控制

•在1和32之间进行乘法和除法

•时钟移位能力

•外部反馈能力

■ 系统IO™ 接口

•1.8、2.5、3.3伏LVCMOS

–可编程阻抗

–热套接

–灵活的总线维护(上拉、下拉、总线保持器或无)

–开式排水操作

•不锈钢2、3(I和II)

•HSTL(I、III、IV)

•PCI 3.3

•GTL+

•等级

•LVPECL公司

•LVTTL

■ 扩展的系统内可编程性(ispXP™)

•即时启动功能

•单芯片方便

•通过IEEE 1532接口进行系统内编程

•通过IEEE 1532或sysCONFIG无限可重新配置™ 微处理器接口

•设计安全

■ 高速运行

•4.0ns针对针延迟,300MHz fMAX

•确定时间

■ 低功耗

•典型静态功率:20至50mA(1.8V),30至60mA(2.5/3.3V)

•1.8V核心,低动态功率

■ 易于系统集成

•3.3V(5000MV)、2.5V(5000MB)和1.8V(5000MC)电源操作

•LVCMOS 3.3和LVTTL接口的5V耐受I/O

•用于边界扫描测试的IEEE 1149.1接口

•sysIO快速配置

•密度迁移

•多种密度和包装选项

•PQFP和细间距BGA封装

•无铅包装选项