AD9510-VCO/PCBZ提供多输出时钟分配功能以及片上锁相环(PLL)核心。该设计强调低抖动和相位噪声,以最大化数据转换器的性能。具有苛刻相位噪声和抖动要求的其他应用也受益于该设备。

PLL部分包括可编程参考分频器(R);低噪声相位频率检测器(PFD);精密电荷泵(CP);通过将外部压控晶体振荡器(VCXO)或压控振荡器(VCO)连接到CLK2和CLK2B引脚,可以将高达1.6GHz的频率与输入基准同步。

有八个独立的时钟输出。四个输出为1.2GHz的低电压正射极耦合逻辑(LVPECL),四个输出可选择为LVDS(800MHz)或CMOS(250MHz)电平。

每个输出都有一个可编程除法器,它可以被旁路或设置为除以最多32的任何整数。一个时钟输出相对于另一时钟输出的相位可以通过用作粗略定时调整的分频器相位选择功能来改变。LVDS/CMOS输出中的两个具有可编程延迟元件,其满量程延迟范围高达8 ns。此微调延迟块具有5位分辨率,为每个满量程设置提供25个可能的延迟选项(寄存器0x36和寄存器0x3A=00000b至11000b)。

AD9510-VCO/PCBZ非常适合于数据转换器时钟应用,其中通过对具有亚皮秒抖动的信号进行编码来实现最大转换器性能。

AD9510-VCO/PCBZ采用64引脚LFCSP,可通过单个3.3V电源进行操作。需要扩展电压范围的外部VCO可通过将充电泵电源(VCP)连接至5.5 V来适应。温度范围为−40°C至+85°C。

特色

- 低相位噪声锁相环磁芯

- 参考输入频率至250 MHz

- 可编程双模预分频器

- 可编程电荷泵(CP)电流

- 单独的CP电源(VCPS)扩展了调谐范围

- 两个1.6 GHz差分时钟输入

- 8个可编程除法器,1至32,所有整数

- 输出至输出粗延迟调整的相位选择

- 4个独立的1.2 GHz LVPECL输出

- 225 fs rms的相加输出抖动

- 4个独立的800MHz低压差分信号

- (LVDS)或250 MHz互补金属氧化物导体

- (CMOS)时钟输出

- 275 fs rms的相加输出抖动

- 2个LVDS/CMOS输出上的精细延迟调整

- 串行控制端口

- 节省空间的64导联LFCSP

应用

- 低抖动、低相位噪声时钟分布

- 时钟高速ADC、DAC、DDS、DDC、DUC和混合信号前端(MxFE)

- 高性能无线收发器

- 高性能仪表

- 宽带基础设施

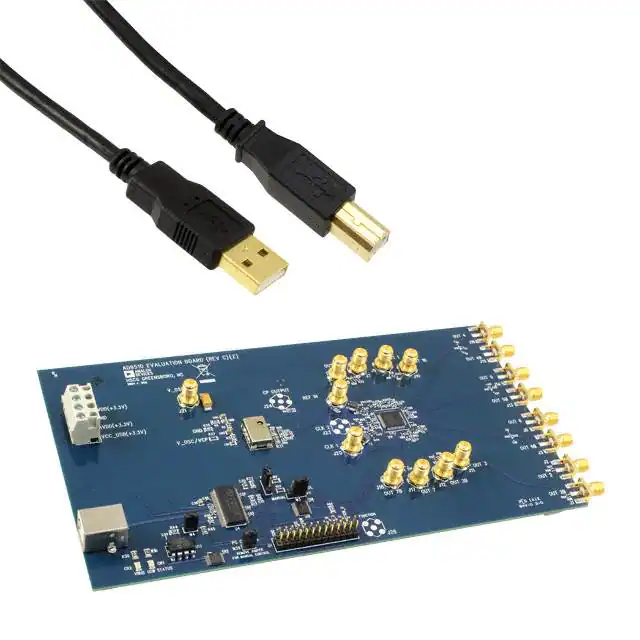

(图片:引出线)