Feature

1.1.1. Solutions

Smallest footprint, lowest power, high data throughput bridging solutions for mobile applications

Optimized footprint, logic density, IO count, IO performance devices for IO management and logic applications

High IO/logic, lowest cost/IO, high IO devices for IO expansion applications

1.1.2. Flexible Architecture

Logic Density ranging from 64 to 9.4K LUT4

High IO to LUT ratio with up to 384 IO pins

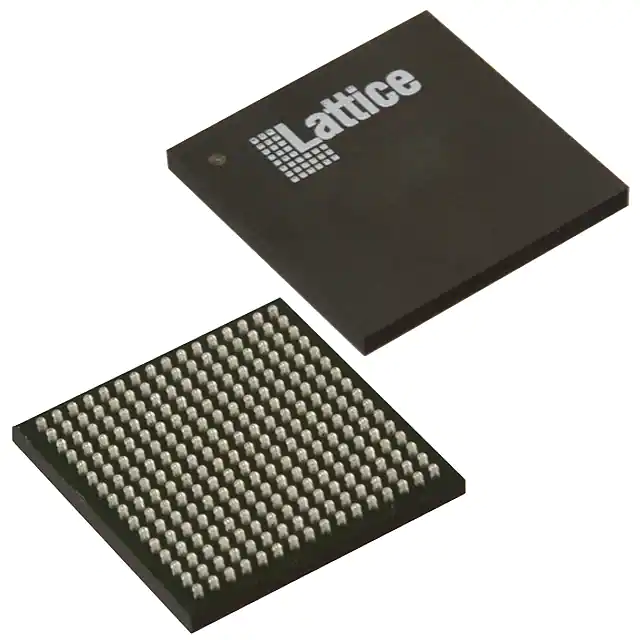

1.1.3. Advanced Packaging

0.4 mm pitch: 1K to 4K densities in very small footprint WLCSP (2.5 mm × 2.5 mm to 3.8 mm × 3.8 mm) with 28 to 63 IOs

0.5 mm pitch: 640 to 9.4K LUT densities in 6 mm x 6 mm to 10 mm x 10 mm BGA packages with up to 281 IOs

0.8 mm pitch: 1K to 9.4K densities with up to 384 IOs in BGA packages

1.1.4. Pre-Engineered Source Synchronous I/O

DDR registers in I/O cells

Dedicated gearing logic

7:1 Gearing for Display I/Os

Generic DDR, DDRx2, DDRx4

1.1.5. High Performance, Flexible I/O Buffer

Programmable sysIO™ buffer supports wide range of interfaces:

LVCMOS 3.3/2.5/1.8/1.5/1.2

LVTTL

LVDS, Bus-LVDS, MLVDS, LVPECL

MIPI D-PHY Emulated

Schmitt trigger inputs, up to 0.5 V hysteresis

Ideal for IO bridging applications

I/Os support hot socketing

On-chip differential termination

Programmable pull-up or pull-down mode

1.1.6. Flexible On-Chip Clocking

Eight primary clocks

Up to two edge clocks for high-speed I/O interfaces (top and bottom sides only)

Up to two analog PLLs per device with fractional-n frequency synthesis

Wide input frequency range (7 MHz to 400 MHz).

1.1.7. Non-volatile, Multi-time Programmable

Instant-on

Powers up in microseconds

Optional dual boot with external SPI memory

Single-chip, secure solution

Programmable through JTAG, SPI or I2C

MachXO3L includes multi-time programmable NVCM

MachXO3LF reconfigurable Flash includes 100,000 write/erase cycle

Supports background programming of non-volatile memory

1.1.8. TransFR Reconfiguration

In-field logic update while IO holds the system state

1.1.9. Enhanced System Level Support

On-chip hardened functions: SPI, I2C, timer/counter

On-chip oscillator with 5.5% accuracy

Unique TraceID for system tracking

Single power supply with extended operating range

IEEE Standard 1149.1 boundary scan

IEEE 1532 compliant in-system programming

Applications

Consumer Electronics

Compute and Storage

Wireless Communications

Industrial Control Systems

Automotive System