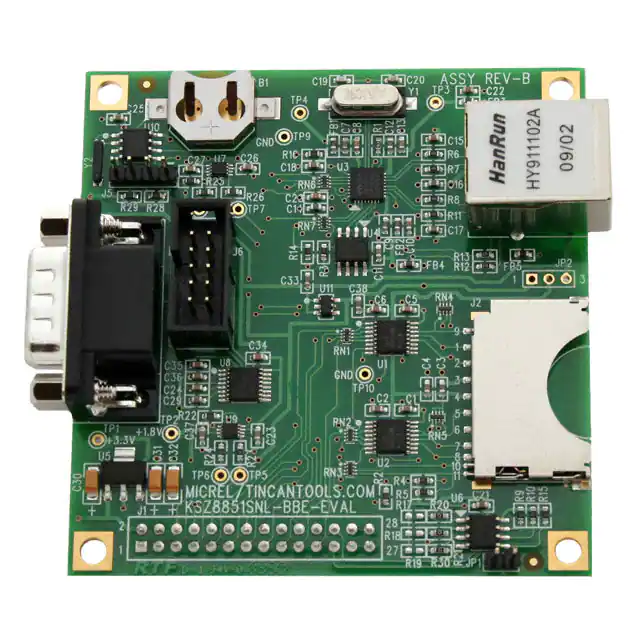

The KSZ8081MNXIA TR is a single-supply 10Base-T/100Base-TX Ethernet physical-layer transceiver for transmission and reception of data over standard CAT-5 unshielded twisted pair (UTP) cable.The KSZ8081MNXIA TR is a highly-integrated PHY solution. It reduces board cost and simplifies board layout by using on-chip termination resistors for the differential pairs and by integrating a low-noise regulator to supply the 1.2V core, and by offering 1.8/2.5/3.3V digital I/O interface support.The KSZ8081RNx offers the Reduced Media Independent Interface (RMII) for direct connection to RMII-compliant MACs in Ethernet processors and switches.As the power-up default, the KSZ8081RNA uses a 25MHz crystal to generate all required clocks, including the 50MHz RMII reference clock output for the MAC. The KSZ8081RND is the version that takes in the 50MHz RMII reference clock as the power-up default. The KSZ8081MLX and KSZ8081MNX offer the Media Independent Interface (MII) for direct connection with MII-compliant Ethernet MAC processors and switches. A 25MHz crystal is used to generate all required clocks.To facilitate system bring-up and debugging in production testing and in product deployment, parametric NAND tree support enables fault detection between KSZ8081RNA I/Os and the board. Microchip's LinkMD® TDR-based cable diagnostics identify faulty copper cabling. The KSZ8081RNA and KSZ8081RND are available in 24-pin, lead-free QFN packages. The KSZ8081MNX and KSZ8081RNB are available in 32-pin, lead-free QFN packages. The KSZ8081MLX is available in 48-pin (7mm x 7mm) LQFP package.Microchip's complimentary and confidential LANCheck® online design review service is available for customers who have selected our products for their application design-in. The LANCheck online design review service is subject to Microchip's Program Terms and Conditions and requires a myMicrochip account.

Feature

- Single-chip 10Base-T/100Base-TX IEEE 802.3 compliant Ethernet transceiver

- MII interface support (KSZ8081MNX)

- RMII v1.2 Interface support with a 50MHz reference clock output to MAC, and an option to input a 50MHz reference clock (KSZ8081RNB)

- RMII back-to-back mode support for a 100Mbps copper repeater

- MDC/MDIO management interface for PHY register configuration

- Programmable interrupt output

- LED outputs for link and activity status indication

- On-chip termination resistors for the differential pairs

- Baseline wander correction

- HP Auto MDI/MDI-X to reliably detect and correct straight-through and crossover cable connections with disable and enable option

- Auto-negotiation to automatically select the highest linkup speed (10/100Mbps) and duplex (half/full)

- Power-down and power-saving modes

- LinkMD® TDR-based cable diagnostics to identify faulty copper cabling

- Parametric NAND Tree support for fault detection between chip I/Os and the board

- Loopback modes for diagnostics

- Single 3.3V power supply with VDD I/O options for 1.8V, 2.5V, or 3.3V

- Built-in 1.2V regulator for core

- Available in 24-pin (4mm x 4mm) QFN package, 32-pin (5mm x 5mm) QFN package or 48-pin (7mm x 7mm) LQFP package