该低偏斜、低抖动设备能够接受高速(例如,622MHz或更高)CML、LVPECL、LVDS或HSTL时钟输入信号,并使用可编程分频器比率来分频频率,以创建输入时钟的较低速度版本。可用的分频器比率为2、4、8和16或直通。差分输入缓冲器具有独特的内部终端设计,允许通过VT引脚访问终端网络。该功能允许设备轻松地与不同的逻辑标准连接。VREF-AC参考包括在交流耦合应用中。/RESET输入异步复位分频器。在直通功能(除以1)中,/RESET同步启用或禁用下一个In下降沿(/In上升沿)的输出。

特色

- 集成可编程时钟分频器和1:2扇出缓冲器

- 温度和电压下的保证交流性能:

- >最大2.0GHz

- <190ps tr/tf

- 设备偏斜内<15ps

- 低抖动设计:

- 总抖动<10pPP

- <1psRMS周期间抖动

- DC和AC耦合输入的唯一输入终端和VTPin;CML、PECL、LVDS和HSTL

- LVDS兼容输出

- 用于选择和重置的TTL/CMOS输入

- 并行编程能力

- 1、2、4、8和16的可编程分频器比率

- 低压运行3.3V

- 输出禁用功能

- -40°C至85°C工业温度范围

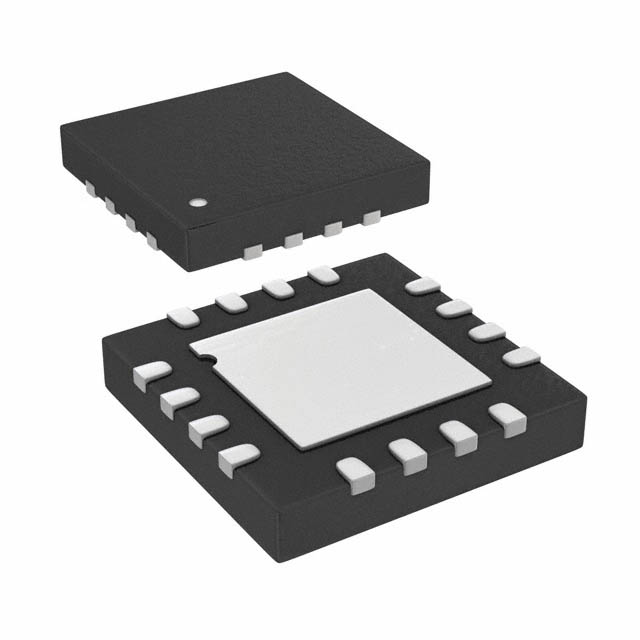

- 提供16针(3mm x 3mm)MLF®封装