49FCT805APYG是使用先进的双金属CMOS技术构建的非反相缓冲器/时钟驱动器。每个银行由两组驾驶员组成。每个存储体从标准TTL兼容输入驱动五个输出缓冲器。这些设备具有用于诊断和PLL驱动的“心跳”监视器。MON输出与所有其他输出相同,并符合本文件中的输出规范。49FCT805APYG提供低电容输入和滞后。轨到轨输出摆动改善了噪声容限,并允许与CMOS输入轻松接口。

特色

- 0.5微米CMOS技术

- 保证低偏斜<700ps(最大值)

- 低占空比失真<1ns(最大值)

- 低CMOS功率电平

- TTL兼容输入和输出

- 轨间输出电压摆动

- 高驱动:-24mA IOH,+64mA IOL

- 具有三态控制的两个独立输出组

- 每排1:5扇出

- “心跳”监视器输出

- 提供SSOP和SOIC封装

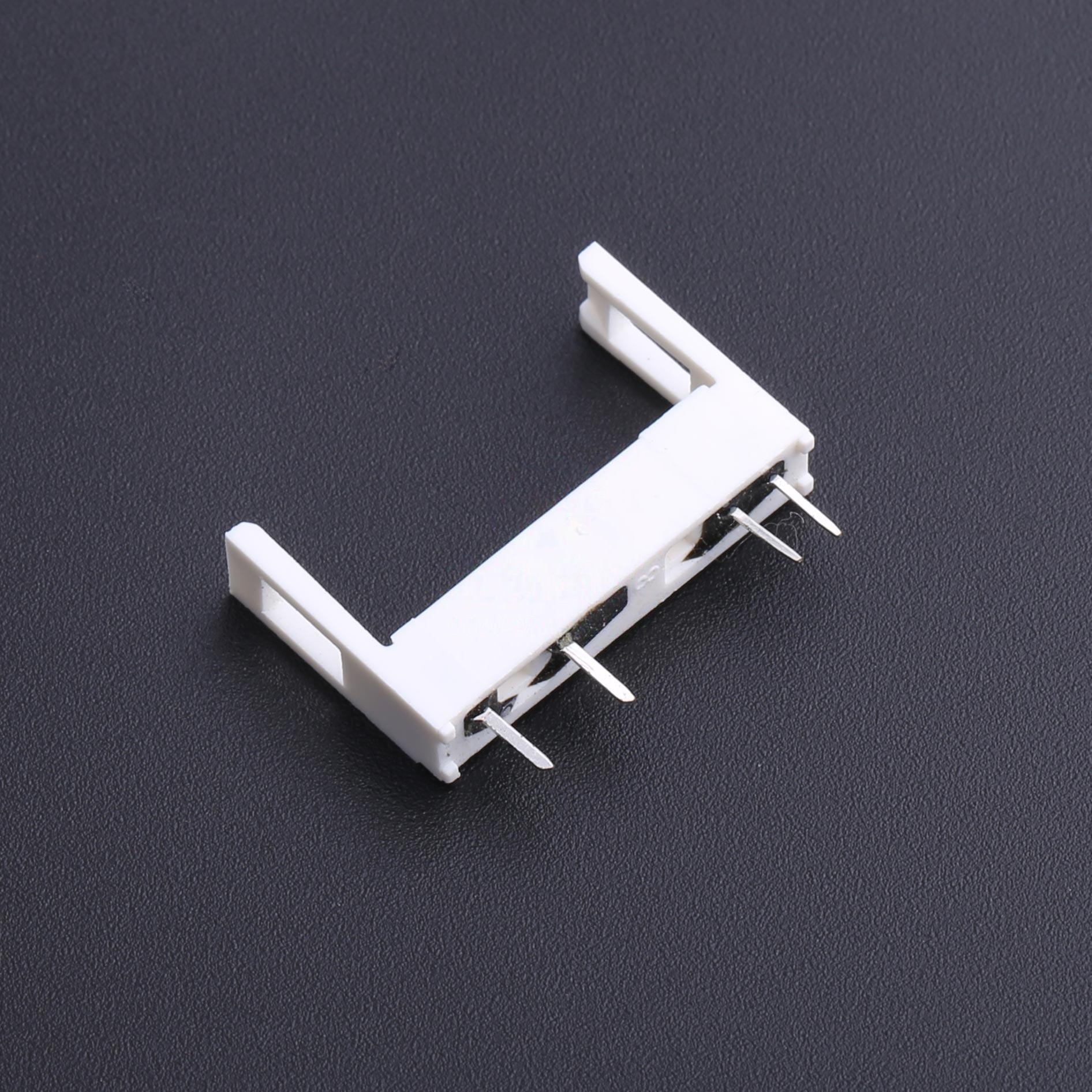

(图片:引出线)