SY89823LHG是一款高性能总线时钟驱动器,具有22个差分高速收发器逻辑(HSTL)、1.5V兼容输出对。该设备设计用于低电压(3.3V/1.8V)应用,需要大量输出以将精确对齐的超低偏斜信号驱动到其目的地。CLK_SEL引脚将输入从HSTL或低压正射极耦合逻辑(LVPECL)多路复用。输出使能(OE)是同步的,并有三重缓冲,因此输出仅在已处于Low状态时才被启用/禁用。这避免了在设备启用/禁用时产生运行时时钟脉冲的任何可能性,如异步控制可能发生的情况。三重缓冲功能提供从OE输入被断言/取消断言到时钟出现在输出端的三个时钟延迟。SY89823LHG具有低引脚对引脚偏斜(最大50ps)和低部件对部件偏斜(最大200ps)的特点,这是以前在具有如此多输出的标准产品中无法实现的性能。SY89823LHG是一个单一的、节省空间的组件,能够实现较低的总体成本解决方案。

特色

- 22个差分HSTL(低压摆动)输出对

- HSTL输出驱动器50Ω接地,无偏置电压

- 3.3V核心电源,1.8V输出电源,降低功率

- LVPECL和HSTL输入

- 低部件间歪斜(最大200ps)

- 低引脚间歪斜(最大50ps)

- 三缓冲输出启用(OE)

- -40°C至+85°C温度范围

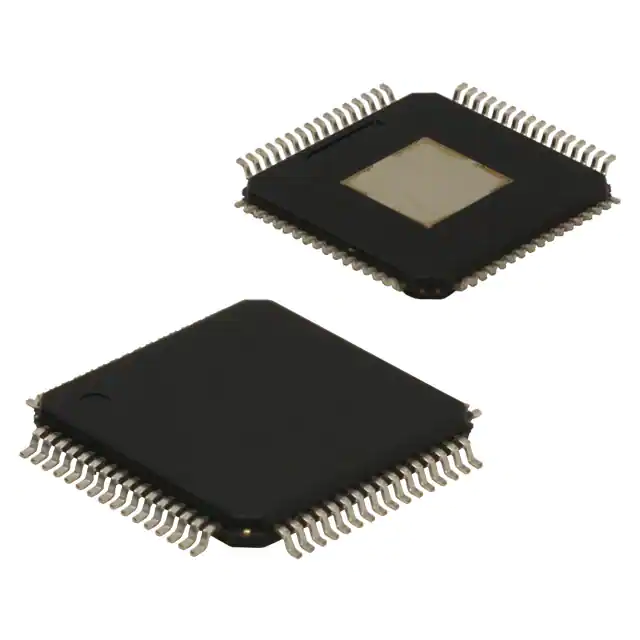

- 提供64针EPAD-TQFP