适用于宽频率覆盖的先进振荡器设计2 LVCMOS输出8 mA输出驱动强度输入/输出频率:o基本晶体:至40MHz极低抖动和相位噪声低电流消耗单至3.63V电源,符合DFN-6L GREEN/RoHS标准封装

说明是一种先进的振荡器扇出缓冲器设计,适用于高性能、低功耗、小尺寸应用。PL135-27GC-R接受40MHz的基本晶体输入,并产生两个相同频率的LVCMOS输出。PL135-27GC-R被设计为适合小x 1.3mm DFN封装,并提供最佳的相位噪声和抖动性能,以及任何可比IC的最低功耗。

Micrel Inc.股份有限公司美国加利福尼亚州圣何塞市财富大道2180号,邮编:95131电话:www.Micrel.com版次:02/14/11第1页

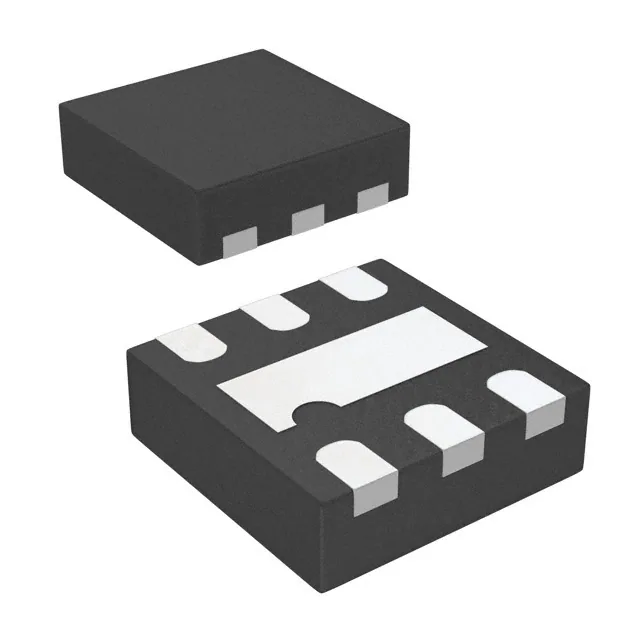

低功率,1:2振荡振荡器扇出缓冲包引脚分配名称XIN CLK1 GND CLK0 VDD XOUT封装引脚#DFN-6L型晶体输入时钟输出GND连接时钟输出VDD连接晶体输出描述

以下指南旨在帮助您进行性能优化的PCB设计:信号完整性和终端注意事项-保持迹线短!-跟踪=电感器。对于电容负载,这等于振铃!-长轨迹=传输线。如果没有适当的终端,这将导致反射(看起来像振铃)。-将长迹线设计为具有定义阻抗的“带状线”或“微带线”在一侧匹配轨迹以避免反射来回反弹。

典型的CMOS终端将串联电阻器尽可能靠近CMOS输出CMOS输出缓冲器(典型的缓冲器阻抗20)至CMOS输入50线

去耦和电源注意事项-将去耦电容器放置在尽可能靠近V DD引脚的位置,以限制来自电源的噪声-应单独去耦多个V DD引脚,以获得最佳性能。-添加与V DD串联的铁氧体磁珠有助于防止来自其他板源的噪声-去耦电容器的值取决于频率。使用0.1 F的典型值。

晶体调谐电路串联和并联电容器,用于根据电路负载微调晶体负载。

串联电阻器使用值将输出缓冲阻抗匹配到50迹线。典型值30CST公司� 串联电容器,用于降低电路负载以匹配晶体负载。提高频率偏移。这可以通过使用Cload值等于或大于振荡器的晶体来消除。运费付至指定目的地� 并联电容器,用于提高电路负载以匹配晶体负载。降低频率偏移。

Micrel Inc.股份有限公司美国加利福尼亚州圣何塞市财富大道2180号,邮编:95131电话:www.Micrel.com版次:02/14/11第2页

低功率,1:2振动台扇出缓冲器电气规范绝对最大额定值参数电源电压范围输入电压范围输出电压范围存储温度环境工作温度*SYMBOL VO TS最小值最大值150 85单位

在超出最大额定值规定的条件下长时间暴露设备可能会对设备造成永久性损坏,并影响产品可靠性。这些条件仅代表应力额定值,不暗示在这些或任何其他条件下装置的功能操作高于本规范中所述的操作极限*工作温度由设计保证。零件仅按商业等级进行测试。

参数晶体输入频率设置时间V DD灵敏度输出上升时间输出下降时间输出到输出倾斜占空比条件基本晶体通电>1.62V)频率vs.V DD,�10%15pF负荷,10/90%V DD,3.3V 15pF负载,90/10%V DD,3.3 V在所有条件下,所有条件下最小10典型值。最大单位MHz ms ppm ps%

参数电源电流,动态符号条件25MHz,空载OH I OSD 25MHz,无负载25MHz,负载工作电压输出低压输出高压输出电流1.62 MIN TYP MAX UNITS V mA

Micrel Inc.股份有限公司美国加利福尼亚州圣何塞市财富大道2180号,邮编:95131电话:www.Micrel.com版次:02/14/11第3页

特色

- 先进的振荡器设计,频率覆盖范围广

- 两个LVCMOS输出

- 8mA输出驱动强度

- 输入/输出频率:10MHz至40MHz基波晶体

- 非常低的抖动和相位噪声

- 低电流消耗

- 单个1.62V至3.63V电源

- 提供2.0mm x 13mm DFN-6L、绿色/RoHS兼容包装