AFE58JD16ZAV是一种高度集成的模拟前端(AFE)解决方案,专门为需要高性能、低功耗和小尺寸的超声系统设计。

请求完整的数据表或其他设计资源:请求AFE58JD16

AFE58JD16ZAV是一款针对医疗超声应用而优化的集成模拟前端(AFE)。AFE58JD16ZAV是一种多芯片模块(MCM)器件,具有两个管芯:VCA和ADC_CONV。每个模具总共有16个通道。

VCA管芯中的每个通道可以配置为两种模式:时间增益补偿(TGC)模式和连续波(CW)模式。在TGC模式下,每个通道包括一个输入衰减器(ATTEN)、一个可变增益的低噪声放大器(LNA)和一个三阶低通滤波器(LPF)。衰减器支持8 dB至0 dB的衰减范围,LNA支持14 dB至45 dB的增益范围。LPF截止频率可以配置为10MHz、15MHz、20MHz或25MHz,以支持具有不同频率的超声应用。在CW模式下,每个信道包括具有18dB固定增益的LNA和具有16个可选择相位延迟的低功率无源混频器。不同的相位延迟可以应用于每个模拟输入信号以执行片上波束形成操作。CW混频器中的谐波滤波器抑制三次和五次谐波,以提高CW多普勒测量的灵敏度。CW模式支持三种时钟模式:16X、8X和4X。

ADC_CONV管芯的每个通道都具有高性能模数转换器(ADC),其可编程分辨率为14位或12位。ADC在14位模式下实现75dBFS的信噪比(SNR),在12位模式下达到72dBFS的SNR。该ADC在低信道增益下提供优异的SNR。该设备以65 MSPS和80 MSPS的最高速度运行,分别提供14位和12位输出。ADC设计成随采样率缩放功率。ADC的输出接口是低电压差分信号(LVDS)或JESD接口,可轻松与低成本现场可编程门阵列(FPGA)连接。

AFE58JD16ZAV在12位或14位ADC之后包括可选的数字解调器和JESD204B数据打包块。具有可编程分数抽取滤波器的数字同相和正交(I/Q)解调器以低功耗加速计算密集型算法。该设备还支持可选的JESD204B接口,该接口可运行高达5 Gbps,并进一步减少了高信道数系统中的电路板布线难题。

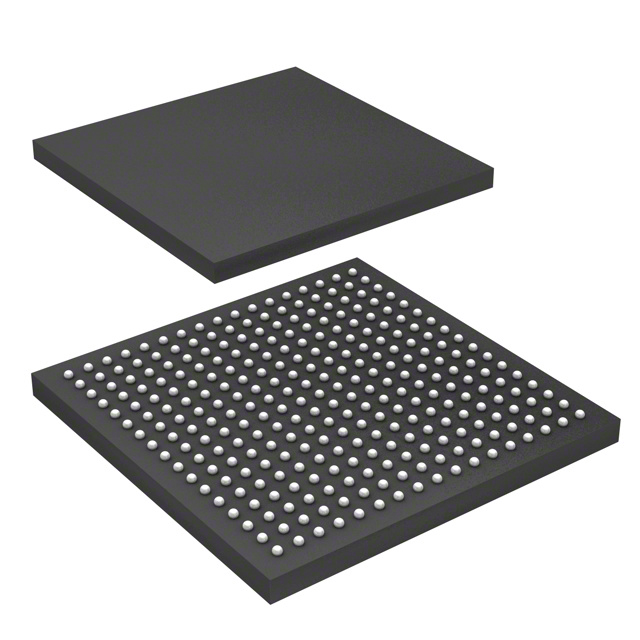

AFE58JD16ZAV还允许选择各种功率和噪声组合,以优化系统性能。因此,这些设备适合于具有严格电池寿命要求的系统的超声AFE解决方案。AFE58JD16ZAV可提供15 mm D7 15 mm NFBGA-289封装(ZAV封装,S-PBGAN289),并指定用于从9640°B0C到+85°B0C的操作。设备引脚也类似于AFE5818系列。

特色

- 超声应用的16通道AFE:

- 输入衰减器、LNA、LPF、ADC和

CW混合器 - 数字时间增益补偿(DTGC)

- 总增益范围:6 dB至45 dB

- 线性输入范围:1 VPP

- 输入衰减器、LNA、LPF、ADC和

- 带DTGC的输入衰减器:

- 8-dB至0-dB衰减,0.125dB阶跃

- 支持匹配阻抗:

- 50Ω至800Ω源阻抗

- 带DTGC的低噪声放大器(LNA):

- 14 dB至45 dB增益,0.125dB阶跃

- 低输入电流噪声:1.2 pA/√Hz

- 三阶线性相位低通滤波器(LPF):

- 10 MHz、15 MHz、20 MHz和25 MHz

- 模数转换器(ADC):

- 14位ADC:65 MSPS时的75 dBFS SNR

- 12位ADC:80 MSPS时的72 dBFS SNR

- LVDS接口,最高速度可达

1 GBPS - 针对噪音和功率进行了优化:

- 90 mW/Ch,1 nV/√Hz,65 MSPS

- 55 mW/Ch,1.45 nV/√Hz,40 MSPS

- CW模式下59 mW/Ch

- 卓越的器件间增益匹配:

- ±0.5 dB(典型)

- 低谐波失真:–60 dBc电平

- 快速且一致的过载恢复

- 连续波(CW)路径:

- 低接近同相噪声–148 dBc/Hz

频率为1kHz - 相位分辨率:λ/16

- 支持16X、8X、4X和1X CW时钟

- 低接近同相噪声–148 dBc/Hz

- 数字功能:

- ADC后的数字I/Q解调器:

- 分数抽取滤波器M=1至63

0.25X增量步长 - 之后数据吞吐量减少

抽取 - 带32个预设配置文件的片上RAM

- 分数抽取滤波器M=1至63

- ADC后的数字I/Q解调器:

- 5 Gbps JESD接口:

- JESD204B子类0、1和2

- 每个JESD通道2、4或8个通道

- 小包装:15 mm×15 mm NFBGA-289