每个信道具有45 dB的可变增益范围、全差分信号路径、有源输入前置放大器终端、最高51 dB的最大增益以及转换率高达65 MSPS的ADC。在小封装尺寸至关重要的应用中,该通道针对动态性能和低功耗进行了优化。

LNA具有可通过SPI选择的单端至差分增益。在21.3 dB的增益下,LNA输入噪声通常为1.3 nV/√Hz,在最大增益下,整个信道的组合输入参考噪声为1.3 nV/√Hz。假设15MHz噪声带宽(NBW)和21.3dB LNA增益,输入SNR大约为88dB。在CW多普勒模式下,每个LNA输出驱动一个I/Q解调器。每个解调器通过具有16个相位设置的SPI具有独立可编程的相位旋转。

AD9278BBCZ需要LVPECL-/COM-/LVDS兼容的采样率时钟以实现全性能操作。许多应用程序不需要外部参考或驱动程序组件。

ADC自动将采样率时钟乘以适当的LVDS串行数据速率。提供了用于捕获输出上的数据的数据时钟(DCO±)和用于发出新输出字节信号的帧时钟(FCO±)触发器。

支持关闭单个通道以延长便携式应用的电池寿命。待机模式选项允许快速通电以进行电源循环。在连续波多普勒操作中,VGA、AAF和ADC断电。TGC路径的功率根据可选的ADC速度功率模式进行缩放。

ADC包含多个旨在最大化灵活性和最小化系统成本的功能,例如可编程时钟、数据对齐和可编程数字测试模式生成。数字测试模式包括内置固定模式、内置伪随机模式和通过串行端口接口输入的自定义用户定义测试模式。

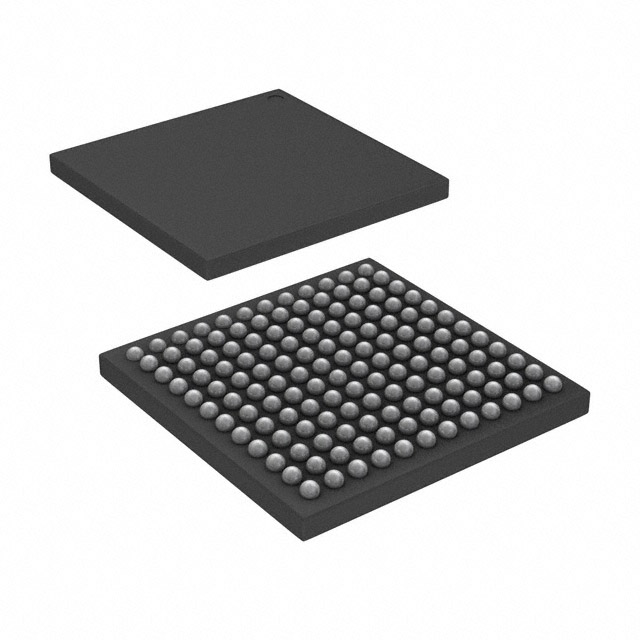

AD9278BBCZ采用先进的BiCMOS工艺制造,尺寸为10mm×10mm,符合RoHS标准,144引线BGA。规定的工业温度范围为-40°C至+85°C。

特色

- 低功耗:每通道88 mW,TGC模式,40 MSPS;每个信道32 mW,CW模式

- 10 mm×10 mm,144球CSP-BGA

- TGC通道输入参考噪声:1.3 nV/√Hz,最大增益

- 灵活的断电模式

- 从低功耗待机模式快速恢复:<2μs

- 过载恢复:<10 ns

- 输入参考噪声:1.25 nV/√Hz,增益=21.3 dB

- 可编程增益:15.6 dB/17.9 dB/21.3 dB

- 0.1 dB压缩:1000 mV p-p/750 mV p-p/450 mV p-p

- 双模有源输入阻抗匹配

- 带宽(BW):>50 MHz

- 衰减器范围:−45 dB至0 dB

- 后置放大器增益(PGA):21 dB/24 dB/27 dB/30 dB

- 线性dB增益控制

- 从8MHz到18MHz的可编程二阶LPF

- 可编程HPF

- 信噪比:70 dB,12位,最高65 MSPS

- 串行LVDS(ANSI-644,低功率/降低信号)

- 单个可编程相位旋转

- 每个通道的输出动态范围:>158 dBc/√Hz

- 输出参考SNR:153 dBc/√Hz,1 kHz偏移,−3dBFS