高动态范围

70 MHz时SNR=75.0 dBFS(AIN=−1 dBFS)

70 MHz时SFDR=87 dBc(AIN=−1 dBFS)

噪声频谱密度(NSD)=−156.7 dBFS/Hz输入噪声

70 MHz时为−1 dBFS

NSD=−157.6 dBFS/Hz,对于70 MHz时−7 dBFS的小信号

90 dB信道隔离/串扰

片上抖动(改善小信号线性)

优异的中频采样性能

170 MHz时SNR=73.7 dBFS(AIN=−1 dBFS)

170 MHz时SFDR=85 dBc(AIN=−1 dBFS)

465 MHz的全功率带宽

片上3.3 V缓冲器

2 V p-p至2.5 V p-p的可编程输入范围(默认值)

具有1、2、4和8整数的差分时钟输入接收器

输入(时钟分频器输入可接受高达1.24 GHz)

内部ADC时钟占空比稳定器

SYNC输入允许多芯片同步

总功耗:2.16 W

3.3 V和1.8 V电源电压

DDR LVDS(ANSI-644电平)输出

串行端口控制

节能省电模式

应用

军用雷达和通信

多模数字接收机(3G或4G)

测试和仪器

智能天线系统

一般说明

AD9652BBCZ-310是一个双16位模数转换器(ADC),采样速度高达310MSPS。它设计用于支持要求苛刻的高速信号处理应用,这些应用需要在宽的输入频率范围(高达465MHz)上具有特殊的动态范围。其出色的低噪声本底为−157.6 dBFS,大信号无杂散动态范围(SFDR)性能(通常超过85 dBFS)允许在存在大信号时分辨低电平信号。

双ADC核心采用多级流水线结构,具有集成输出纠错逻辑。高性能片上缓冲器和内部电压基准简化了与外部驱动电路的接口,同时保持了ADC的卓越性能。

AD9652BBCZ-310可通过1、2、4和8整数分频器支持高达1.24 GHz的输入时钟频率,以生成ADC采样时钟。提供占空比稳定器以补偿ADC时钟占空比的变化。

特色

- 高动态范围-70 MHz时SNR=75.0 dBFS(AIN=−1 dBFS)-70 MHz下SFDR=87 dBc

- 卓越的中频采样性能-170 MHz时SNR=73.7 dBFS(AIN=−1 dBFS)-170 MHz下SFDR=85 dBc(AIN=−1 dBFS)-465 MHz的全功率带宽

- 片上3.3 V缓冲器-可编程输入范围为2 V p-p至2.5 V p-p(默认值)

- 具有1、2、4和8个整数输入的差分时钟输入接收器(时钟分频器输入可接受高达1.24 GHz)

- 内部ADC时钟占空比稳定器

- SYNC输入允许多芯片同步

- 总功耗:2.16 W-3.3 V和1.8 V电源电压

- DDR LVDS(ANSI-644电平)输出

- 串行端口控制

- 节能省电模式

应用

- 军用雷达和通信

- 多模数字接收机(3G或4G)

- 测试和仪器

- 智能天线系统

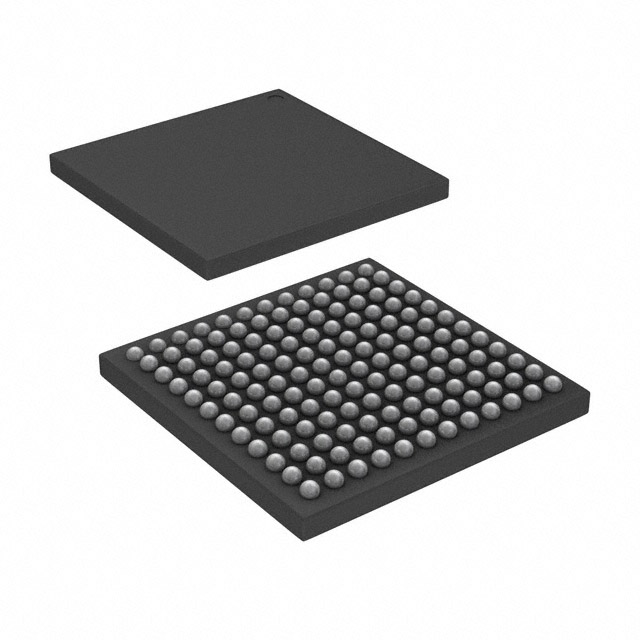

(图片:引出线)