ADC包含多个旨在最大化灵活性和最小化系统成本的功能,例如可编程时钟和数据对齐以及可编程数字测试模式生成。可用的数字测试模式包括内置确定性和伪随机模式,以及通过串行端口接口(SPI)输入的自定义用户定义测试模式。

差分时钟输入控制所有内部转换周期。可选的占空比稳定器(DCS)可补偿时钟占空比的广泛变化,同时保持出色的整体ADC性能。

数字输出数据以偏移二进制、格雷码或二进制补码格式显示。为每个ADC通道提供数据输出时钟(DCO),以确保与接收逻辑的适当锁存定时。支持1.8 V CMOS或LVDS的输出逻辑电平。输出数据也可以复用到单个输出总线上。

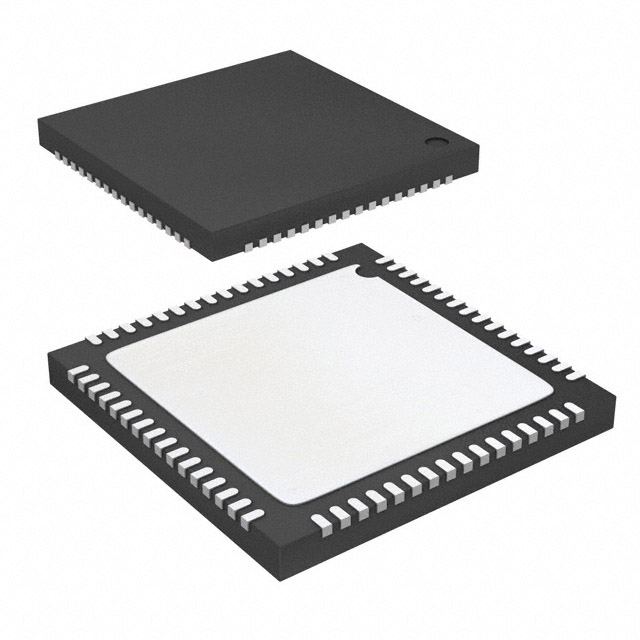

AD9648采用符合RoHS标准的64引脚LFCSP,并在工业温度范围(-40°C至+85°C)内指定。

特色

- 1.8 V模拟电源操作

- 1.8 V CMOS或LVDS输出

- 70 MHz时SNR=74.5 dBFS

- 70 MHz时SFDR=91 dBc

- 低功率:106 mW/信道,125 MSPS

- 650 MHz带宽的差分模拟输入

- 中频采样频率至200 MHz

- 有关其他功能,请参阅数据表

- 下载(pdf)

- 军用温度范围:−55°C至+125°C

- 受控制造基线

- 根据要求提供资格数据

- V62/16606 DSCC图纸编号

应用

- 通信

- 分集无线电系统

- 多模数字接收机GSM、EDGE、W-CDMA、LTE、CDMA2000、WiMAX、TD-SCDMA

- I/Q解调系统

- 智能天线系统

- 宽带数据应用

- 电池供电仪器

- 手持式示波器

- 便携式医学成像

- 超声波

- 雷达/激光雷达

产品亮点

(图片:引出线)