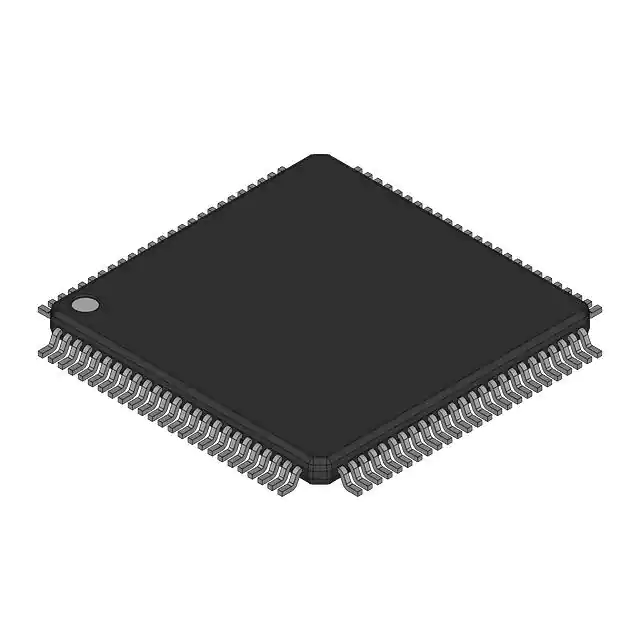

MAX 5000可擦除可编程逻辑器件(EPLD)的EPM5016LI-20代表了可编程逻辑的革命性一步:它们结合了创新的体系结构和最先进的工艺,提供了最佳性能、逻辑密度、灵活性以及通用可编程逻辑中可用的最高速度和密度。这些EPLD是Ss1和MSI TTL和CMOS封装以及传统PLD的高速、高密度替代品。例如,EPM5192取代了100多个7400系列SSI和MSI TTL和CMOS封装,将完整的子系统集成到单个封装中,节省了电路板面积,并降低了功耗。

特色

完整的CMOS EPLD系列解决了从快速20引脚地址解码器到100引脚LSI定制外设的设计任务。

先进的MAX 5000架构将PAL设备的速度、易用性和熟悉性与可编程门阵列的密度相结合。

MAX 5000 EPLD提供15 ns组合延迟、高达100 MHz的计数器频率、100 MHz的流水线数据速率和高复杂度设计,真实系统时钟速率高达66 MHz。

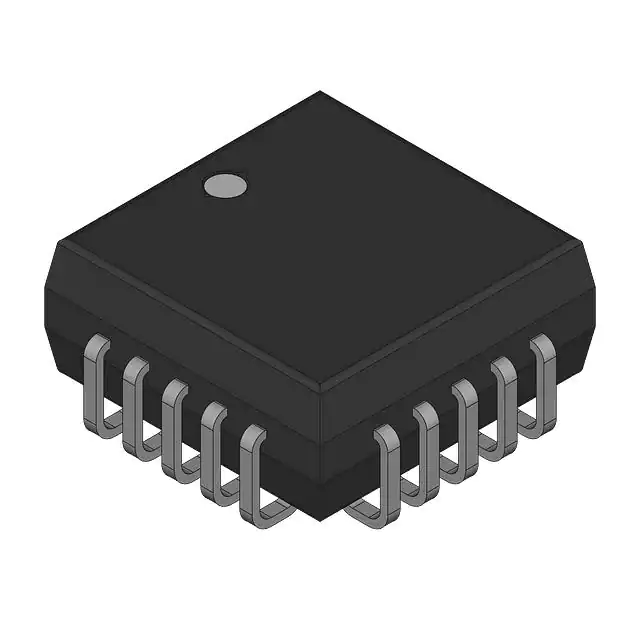

可提供多种封装,包括DIP、SOIC、J型引线、PGA和QFP格式的开窗陶瓷和塑料一次性可编程版本。

MAX+PLUS和MAX+PlusII基于PC和工作站的开发工具可在几分钟内编译大型设计。

工作站和第三方CAE工具的行业标准EDIF接口可用。