描述

MAX 7000系列高密度、高性能PLD基于Altera的第二代MAX架构。基于EEPROM的MAX 7000系列采用先进的CMOS技术制造,可提供600至5000个可用门、ISP、快至5 ns的管脚到管脚延迟和高达175.4 MHz的计数器速度。-5、-6、-7和-10速度等级的MAX 7000S设备以及-5、-6、-7、-10P和-12P速度等级的MAX7000和MAX 7000E设备符合PCI特殊兴趣组(PCI SIG)PCI本地总线规范第2.2版。可用速度等级见表3。

MAX 7000E设备包括EPM7128E、EPM7160E、EPD7192E和EPM7256E设备,具有几个增强功能:额外的全局时钟、额外的输出启用控制、增强的互连资源、快速输入寄存器和可编程转换速率。

称为MAX 7000S设备的系统内可编程MAX 7000设备包括EPM7032S、EPM7064S、EPM7128S、EPC7160S、EPD7192S和EPM7256S设备。MAX 7000S器件具有MAX 7000E器件的增强功能,以及具有128个或更多宏小区、ISP和开放漏极输出选项的器件中的JTAG BST电路。见表4。

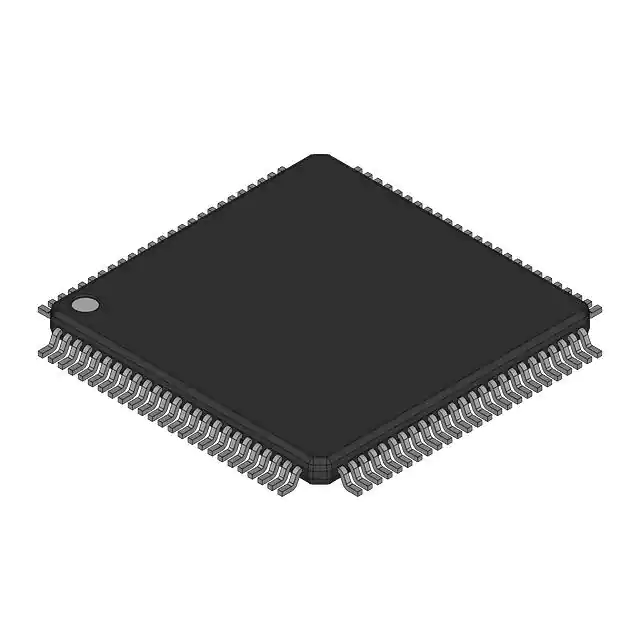

MAX 7000体系结构支持100%TTL仿真和SSI、MSI和LSI逻辑功能的高密度集成。MAX 7000架构可轻松集成从PAL、GAL和22V10到MACH和pLSI设备的多个设备。MAX 7000器件有多种封装,包括PLCC、PGA、PQFP、RQFP和TQFP封装。见表5。

MAX 7000设备使用CMOS EEPROM单元来实现逻辑功能。用户可配置的MAX 7000架构适应各种独立的组合和顺序逻辑功能。在设计开发和调试周期内,可以对设备进行重新编程,以实现快速高效的迭代,并且可以编程和擦除多达100次。

MAX 7000设备包含32到256个宏单元,这些宏单元被组合成16个宏单元的组,称为逻辑阵列块(LAB)。每个宏单元都有一个可编程AND/固定OR阵列和一个可配置寄存器,具有独立可编程时钟、时钟启用、清除和预设功能。为了构建复杂的逻辑功能,每个宏单元可以补充可共享的扩展器产品项和高速并行扩展器产品项,以提供每个宏单元最多32个产品项。

MAX 7000系列提供可编程速度/功率优化。设计的速度关键部分可以在高速/满功率下运行,而其余部分以降低的速度/低功率运行。此速度/功率优化功能使设计者能够配置一个或多个宏小区以50%或更低的功率运行,同时仅添加标称定时延迟。MAX 7000E和MAX 7000S设备还提供了一种选项,可降低输出缓冲器的转换速率,从而在切换非速度关键信号时最小化噪声瞬变。所有MAX 7000设备(44引脚设备除外)的输出驱动器可设置为3.3V或5.0V操作,允许MAX 7000设备用于混合电压系统。

MAX 7000系列由Altera开发系统支持,Altera开发软件是集成的软件包,提供原理图、文本(包括VHDL、Verilog HDL和Altera硬件描述语言(AHDL))和波形设计输入、编译和逻辑合成、仿真和时序分析以及设备编程。该软件提供EDIF 2 0 0和3 0 0、LPM、VHDL、Verilog HDL和其他接口,用于其他基于行业标准PC和UNIX工作站的EDA工具的额外设计输入和仿真支持。该软件在基于Windows的PC、Sun SPARCstation和HP 9000系列700/800工作站上运行。

特色

■ 基于第二代MAX®架构的高性能、基于EEPROM的可编程逻辑器件(PLD)

■ 通过内置IEEE标准1149.1联合测试行动小组(JTAG)实现5.0-V系统内可编程性(ISP)

MAX 7000S设备中可用的接口–ISP电路与IEEE标准1532兼容

■ 包括5.0-V MAX 7000设备和基于5.0-V ISP的MAX 7000S设备

■ MAX7000S器件中内置JTAG边界扫描测试(BST)电路,具有128个或更多宏单元

■ 完整的EPLD系列,逻辑密度从600到5000可用门(见表1和表2)

■ 5-ns管脚到管脚逻辑延迟,计数器频率高达175.4MHz(包括互连)

■ PCI兼容设备可用

■ MAX 7000S设备中的开漏输出选项

■ 具有单独清除、预设、时钟和时钟启用控制的可编程宏单元触发器

■ 可编程节能模式,每个宏小区的能耗降低50%以上

■ 可配置的扩展器产品术语分布,允许每个宏单元最多32个产品术语

■ 44至208个引脚可用于塑料J形引线芯片载体(PLCC)、陶瓷引脚栅格阵列(PGA)、塑料四边形扁平封装(PQFP)、电源四边形扁平包装(RQFP)和1.0毫米薄四边形扁平包(TQFP)封装

■ 用于保护专有设计的可编程安全位

■ 3.3V或5.0V操作

■ MAX 7000E和MAX 7000S设备中提供的增强功能

■ Altera的开发系统为基于Windows的PC、Sun SPARCstation和HP 9000系列700/800工作站提供软件设计支持和自动放置和路由

■ EDIF 2 0 0和3 0 0网表文件、参数化模块库(LPM)、Verilog HDL、VHDL以及制造商(如Cadence、Exemplar Logic、Mentor Graphics、OrCAD、Synopsys和VeriBest)流行EDA工具的其他接口提供了额外的设计输入和模拟支持

■ 编程支持

特色

■ 通过内置IEEE标准1149.1联合测试行动组(JTAG)接口实现5.0 V系统内可编程性(ISP),可用于MAX 7000S设备

–ISP电路与IEEE标准1532兼容

■ 包括5.0-V MAX 7000设备和基于5.0-V ISP的MAX 7000S设备

■ MAX7000S器件中内置JTAG边界扫描测试(BST)电路,具有128个或更多宏单元

(图片:引出线)