说明:

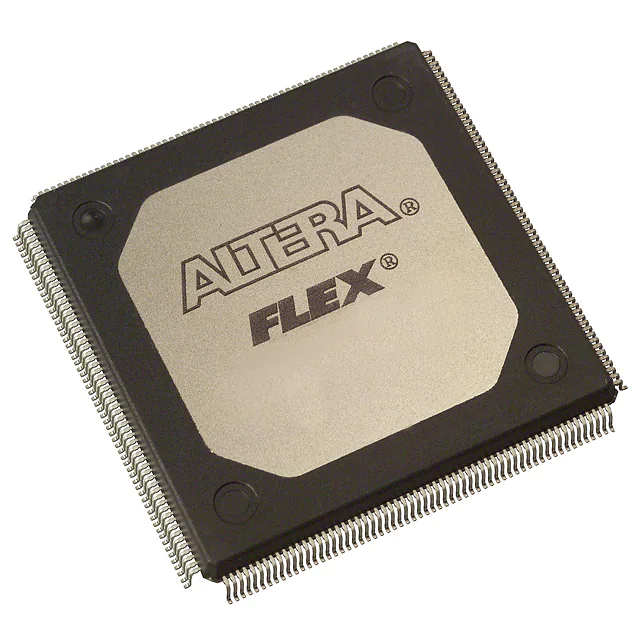

MAX9000系列由Altera的MAX+PLUS II开发系统支持,这是一个单一的集成软件包,提供原理图、文本(包括VHDL、Verilog HDL和Altera硬件描述语言(AHDL))和波形设计输入、编译和逻辑合成、仿真和时序分析以及设备编程。MAX+PLUS II软件提供EDIF200和300、LPM和其他接口,用于其他基于工业标准PC和UNIX工作站的EDA工具的额外设计输入和仿真支持。MAX+PLUS II软件在基于Windows的PC以及Sun SPARCstation、HP 9000系列700/800和IBM RISC System/6000工作站上运行。有关开发工具的更多信息,请参阅MAX+PLUS II可编程逻辑开发系统和软件数据表。MAX9000设备采用第三代MAX架构,可为大多数应用提供高性能和高利用率。MAX 9000架构包括以下元素:逻辑阵列块宏单元扩展器产品术语(可共享和并行)FastTrack互连专用输入I/O单元图1显示了MAX 9000架构的框图。

特征:

基于CMOS EEPROM的高性能可编程逻辑器件(PLD),通过内置IEEE标准1149.1联合测试行动组(JTAG)接口构建在第三代多阵列矩阵((MAXe)体系结构5.0-V的系统可编程性(ISP)上

■ 符合IEEE标准1149.1-1990的内置JTAG边界扫描测试(BST)电路

■ 高密度可擦除可编程逻辑器件(EPLD)系列,可用门数从6000到12000(见表1)

■ 10 ns管脚到管脚逻辑延迟,计数器频率高达

144兆赫

■ 完全符合外围组件互连特殊利益集团(PCI SIG)PCI本地总线规范2.2版

■ 双输出宏单元,可独立使用组合逻辑和注册逻辑FastTracke互连,实现快速、可预测的互连延迟输入/输出寄存器,所有I/O引脚上都有清晰和时钟启用可编程输出转换速率控制,以降低开关噪声MultiVolt“”I/O接口操作,允许设备与

3.3-V和5.0-V设备可配置扩展器产品期限分布,最多允许32个

每个宏单元的乘积项

■ 可编程节能模式,每个宏小区的功耗降低50%以上

特色

基于第三代多阵列矩阵(MAX®)架构的高性能CMOS EEPROM可编程逻辑器件(PLD)

■ 通过内置IEEE标准1149.1联合测试行动组(JTAG)接口实现5.0-V系统内可编程性(ISP)

■ 符合IEEE标准1149.1-1990的内置JTAG边界扫描测试(BST)电路

■ 高密度可擦除可编程逻辑器件(EPLD)系列,可用门数从6000到12000(见表1)

■ 10 ns管脚到管脚逻辑延迟,计数器频率高达144 MHz

■ 完全符合外围组件互连特殊利益集团(PCI SIG)PCI本地总线规范2.2版

■ 用于独立使用组合逻辑和注册逻辑的双输出宏单元

■ FastTrack®互连可实现快速、可预测的互连延迟

■ 输入/输出寄存器,在所有I/O引脚上具有清除和时钟启用功能

■ 可编程输出转换速率控制,降低开关噪声

■ 多电压™ I/O接口操作,允许设备与3.3-V和5.0-V设备接口

■ 可配置的扩展器产品术语分布,允许每个宏单元最多32个产品术语

■ 可编程节能模式,每个宏小区的功耗降低50%以上