特色

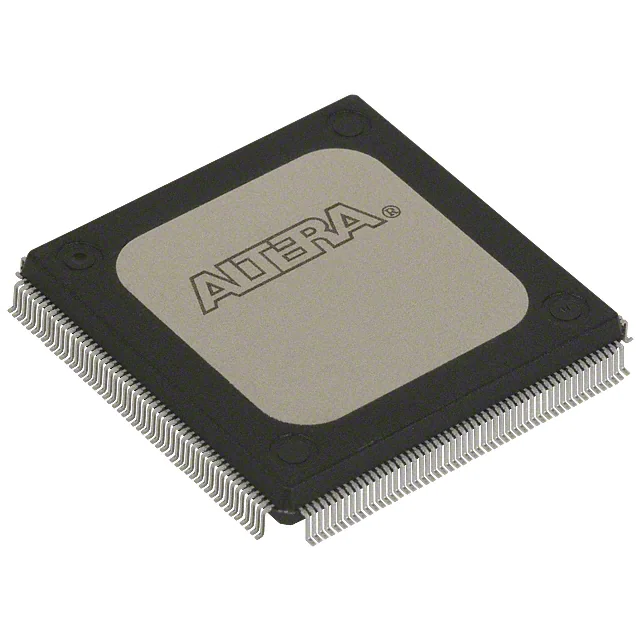

■ 基于CMOS EEPROM的高性能可编程逻辑

基于第三代Multiple Array MatrixX构建的设备(PLD)

(MAX®)体系结构

■ 通过内置IEEE标准的5.0 V系统可编程性(ISP)。

1149.1联合测试行动小组(JTAG)接口

■ 符合IEEE标准的内置JTAG边界扫描测试(BST)电路

标准1149.1-1990

■ 高密度可擦除可编程逻辑器件(EPLD)系列

从6000到12000个可用闸门(见表1)

■ 10 ns管脚到管脚逻辑延迟,计数器频率高达

144兆赫

■ 完全符合外围组件互连专用

利益集团(PCI SIG)PCI本地总线规范,版本2.2

■ 双输出宏单元,可独立使用组合和

寄存逻辑

■ FastTrack®互连可实现快速、可预测的互连延迟

■ 输入/输出寄存器,在所有I/O引脚上具有清除和时钟启用功能

■ 可编程输出转换速率控制,降低开关噪声

■ 多电压™ I/O接口操作,允许设备与

3.3-V和5.0-V设备

■ 可配置的扩展器产品期限分布,最多允许32个

每个宏单元的乘积项

■ 可编程节能模式,功率超过50%

每个宏小区的减少

基于第三代Multiple Array MatrixX构建的设备(PLD)

(MAX®)体系结构

■ 通过内置IEEE标准的5.0 V系统可编程性(ISP)。

1149.1联合测试行动小组(JTAG)接口

■ 符合IEEE标准的内置JTAG边界扫描测试(BST)电路

标准1149.1-1990

■ 高密度可擦除可编程逻辑器件(EPLD)系列

从6000到12000个可用闸门(见表1)

■ 10 ns管脚到管脚逻辑延迟,计数器频率高达

144兆赫

■ 完全符合外围组件互连专用

利益集团(PCI SIG)PCI本地总线规范,版本2.2

■ 双输出宏单元,可独立使用组合和

寄存逻辑

■ FastTrack®互连可实现快速、可预测的互连延迟

■ 输入/输出寄存器,在所有I/O引脚上具有清除和时钟启用功能

■ 可编程输出转换速率控制,降低开关噪声

■ 多电压™ I/O接口操作,允许设备与

3.3-V和5.0-V设备

■ 可配置的扩展器产品期限分布,最多允许32个

每个宏单元的乘积项

■ 可编程节能模式,功率超过50%

每个宏小区的减少