特色

·最高性能浮点数字信号处理器(DSP):TMS320C6713B

−八个32位指令/周期−32/64位数据字

−300、225、200 MHz(GDP和ZDP)和225、200、167 MHz(PYP)时钟频率

−3.3-、4.4-、5-、6-指令循环时间

−2400/1800、1800/1350、1600/1200和1336/1000 MIPS/MFLOPS

−丰富的外围设备集,针对音频进行了优化

−高度优化的C/C++编译器

−可用的扩展温度设备

·高级超长指令字(VLIW)TMS320C67x 数字信号处理器内核

−八个独立功能单元:

−2个ALU(定点)

−4个ALU(浮点/定点)

−2个乘法器(浮点/定点)

−具有32位通用寄存器的加载存储架构

−指令打包减少代码大小

−所有有条件的指令

·指令集功能

−IEEE 754的本地指令

−单精度和双精度

−字节可寻址(8位、16位、32位数据)

−8位溢出保护

−饱和;位字段提取、设置、清除;位计数;规范化

·L1/L2存储器体系结构

−4K字节L1P程序缓存(直接映射)

−4K字节L1D数据缓存(双向)

−256K字节的二级内存总量:64K字节二级统一缓存/映射RAM,192K字节附加二级映射RAM

·设备配置

−引导模式:HPI、8位、16位、32位ROM引导

−无尽:小无尽、大无尽

·32位外部存储器接口(EMIF)

−SRAM、EPROM、闪存、SBSRAM和SDRAM的无胶接口

−512M字节总可寻址外部内存空间

·增强型直接存储器存取(EDMA)控制器(16个独立信道)

·16位主机端口接口(HPI)

·两个McASP

−两个独立的时钟区(1个TX和1个RX)

−每个端口八个串行数据引脚:可单独分配给任何时钟区

−每个时钟区包括:

−可编程时钟发生器

−可编程帧同步发生器

−来自2-32个时隙的TDM流

−支持插槽大小:8、12、16、20、24、28、32位

−用于位操作的数据格式化程序

−多种I2S和类似比特流格式

−集成数字音频接口发射机(DIT)支持:

−S/PDIF、IEC60958-1、AES-3、CP-430格式

−最多16个传输引脚

−增强的信道状态/用户数据

−广泛的错误检查和恢复

·两个内部集成电路总线(I2C总线) 多主/从接口

·两个多通道缓冲串行端口:

−串行外围接口(SPI)

−高速TDM接口

−AC97接口

·两个32位通用定时器

·具有16个引脚的专用GPIO模块(支持外部中断)

·基于灵活锁相环(PLL)的时钟发生器模块

·IEEE-1149.1(JTAG†)边界扫描兼容

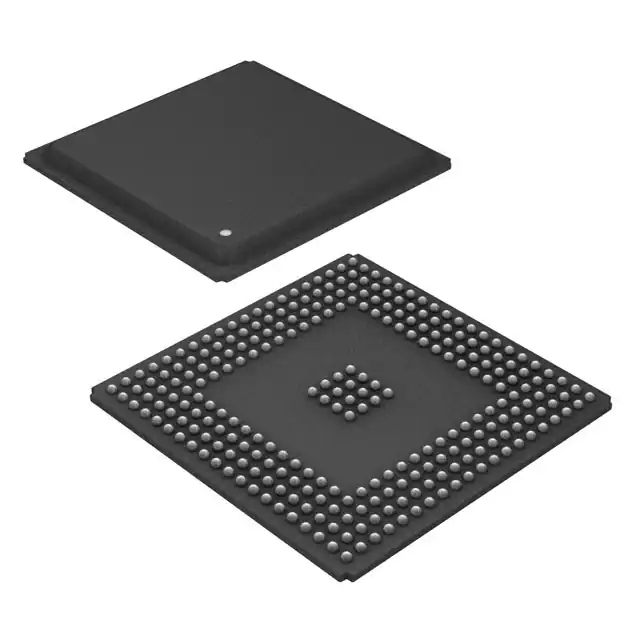

·208针PowerPAD PQFP(PYP)

·272-BGA包(GDP和ZDP)

·0.13-µm/6级铜金属工艺

−CMOS技术

·3.3-V I/O,1.2‡-V内部(GDP/ZDP/PYP)

·3.3V I/O,1.4V内部(GDP/ZDP)[300 MHz]

特色

- 最高性能浮点数字信号处理器(DSP):TMS320C6713B

- 八个32位指令/周期

- 32/64位数据字

- 300、225、200 MHz(GDP和ZDP)和225、200、167 MHz(PYP)时钟频率

- 3.3-、4.4-、5-、6-指令循环时间

- 2400/1800、1800/1350、1600/1200和1336/1000 MIPS/MFLOPS

- 丰富的外围设备集,针对音频进行了优化

- 高度优化的C/C++编译器

- 可用的扩展温度设备

- 高级超长指令字(VLIW)TMS320C67x DSP内核

- 八个独立功能单元:

- 2个ALU(定点)

- 4个ALU(浮点/定点)

- 2个乘法器(浮点/定点)

- 具有32位通用寄存器的加载存储体系结构

- 指令打包减少代码大小

- 所有有条件的指令

- 八个独立功能单元:

- 指令集功能

- IEEE 754的本机指令

- 单精度和双精度

- 可寻址字节(8位、16位、32位数据)

- 8位溢出保护

- 饱和位字段提取、设置、清除;位计数;规范化

- IEEE 754的本机指令

- L1/L2存储器体系结构

- 4K字节L1P程序缓存(直接映射)

- 4K字节L1D数据缓存(双向)

- 256K字节的二级内存总计:64K字节二级统一缓存/映射RAM和192K字节附加二级映射RAM

- 设备配置

- 引导模式:HPI、8位、16位、32位ROM引导

- 无尽:小无尽,大无尽

- 32位外部存储器接口(EMIF)

- SRAM、EPROM、闪存、SBSRAM和SDRAM的无胶接口

- 512M字节的总可寻址外部内存空间

- 增强型直接存储器存取(EDMA)控制器(16个独立信道)

- 16位主机端口接口(HPI)

- 两个McASP

- 两个独立的时钟区(1个TX和1个RX)

- 每个端口八个串行数据引脚:可单独分配给任何时钟区

- 每个时钟区包括:

- 可编程时钟发生器

- 可编程帧同步发生器

- 来自2-32时隙的TDM流

- 支持插槽大小:

-

8、12、16、20、24、28、32位

- 用于位操作的数据格式化程序

- 多种I2S和类似的比特流格式

- 集成数字音频接口发射机(DIT)支持:

- S/PDIF、IEC60958-1、AES-3、CP-430格式

- 最多16个传输引脚

- 增强的频道状态/用户数据

- 广泛的错误检查和恢复

- 两个集成电路间总线(I2C总线)多主从接口

- 两个多通道缓冲串行端口:

- 串行外围接口(SPI)

- 高速TDM接口

- AC97接口

- 两个32位通用定时器

- 具有16个引脚的专用GPIO模块(支持外部中断)

- 基于灵活锁相环(PLL)的时钟发生器模块

- IEEE-1149.1(JTAG)边界扫描兼容

- 208针PowerPAD PQFP(PYP)

- 272-BGA包(GDP和ZDP)

- 0.13-μm/6级铜金属工艺

- CMOS技术

- 3.3-V I/O,1.2-V内部(GDP/ZDP/PYP)

- 3.3V I/O,1.4V内部(GDP/ZDP)[300 MHz]

(图片:引出线)