特征

•高性能达芬奇视频处理器

–高达1GHz ARM®Cortex®-A8 RISC核心

–最高750 MHz C674x™ VLIW数字信号处理器

–最高6000 MIPS和4500 MFLOPS

–与C67x完全软件兼容+™,

C64倍+™

•ARM Cortex-A8内核

–ARMv7体系结构

•有序、双问题、超标量

处理器核心

•霓虹灯™ 多媒体体系结构

•支持整数和浮点

•Jazelle®RCT执行环境

•ARM Cortex-A8内存架构

–32KB的指令和数据缓存

–512KB的二级缓存

–64KB RAM,48KB引导ROM

•TMS320C674x浮点VLIW DSP

–64个通用寄存器(32位)

–六个ALU(32-/40位)功能单元

•支持32位整数、SP(IEEE单

精度/32位)和DP(IEEE Double

精度/64位)浮点

•每个时钟最多支持四个SP添加,每两个时钟支持四个DP添加

•每个周期最多支持两个浮点(SP或DP)近似倒数或平方根运算

–两个乘法功能单元

•混合精度IEEE浮点

支持的乘法最多:

–2 SP x SP→ 每时钟SP

–2 SP x SP→ DP每两个时钟

–2 SP x DP→ DP每三个时钟

–2 DP x DP→ DP每四个时钟

•定点乘法支持两个32 x 32乘法、四个16 x 16位乘法(包括复数乘法)或每个时钟周期八个8 x 8位乘法

•C674x两级内存架构

–32KB L1P RAM/缓存,带EDC

–32KB的L1D RAM/缓存

–256KB带ECC的二级统一映射RAM/缓存

•系统内存管理单元(MMU)

–映射C674x DSP和EDMA TC内存

访问系统地址

•128KB片上存储器控制器(OCMC)RAM

•成像子系统(ISS)

–摄像头传感器连接处理器核心

•Raw(最多16位)和BT.656或BT.1120(8位和16位)的并行连接

–图像传感器接口(ISIF),用于处理来自摄像机传感器的图像和视频数据

–调整大小

•将图像和视频大小从1/16倍调整为8倍

•同时生成两个不同的调整输出

•可编程高清视频图像协同处理(HDVICP v2)引擎

–编码、解码、转码操作

–H.264、MPEG-2、VC-1、MPEG-4、SP/ASP、JPEG/MJPEG

•媒体控制器

–控制HDVPSS、HDVICP2和ISS

•SGX530 3D图形引擎

–提供敢达25 MPoly/秒

–通用可扩展着色器引擎

–Direct3D Mobile、OpenGLES 1.1和2.0、OpenVG 1.0、OpenMax API支持

–高级几何DMA驱动操作

–可编程HQ图像消除混叠

•持久性

–ARM和DSP指令/数据–Little Endian

•高清视频处理子系统(HDVPSS)

–两个165 MHz、2通道高清视频捕获模块

•一个16-/24位输入或双8位SD输入通道

•一个8-/16-24位输入和一个仅8位输入通道

–两个165 MHz高清视频显示输出

•一个16位、24位或30位输出和一个16-24位输出

–复合或S-Video模拟输出

–提供Macrovision®支持

–数字HDMI 1.3发射机,内置

–高级视频处理功能,如扫描、格式、速率转换

–三个图形层和合成器

•双32位DDR2/DDR3 SDRAM接口

–最多支持DDR2-800和DDR3-1066

–最多8 x 8个设备,总2GB(总48 MHz)地址空间

–动态内存管理器(DMM)

•可编程多区存储器映射和交织

•实现高效的2D块访问

•支持0°、90°、180°或270°方向的平铺对象和镜像

•四个内部集成电路(I2C总线)端口

•优化交错访问

•通用内存控制器(GPMC)

–8位或16位多路复用地址和数据端口总线

–512MB的地址空间在多达8个芯片选择的端口之间分配

–NOR闪存、NAND闪存(BCH/Hamming错误代码检测)、SRAM和伪SRAM的无胶接口

–GPMC外部的错误定位模块(ELM)可提供多达16位或512字节的支持TDM、I2S和类似格式的NAND硬件ECC

–灵活的异步协议控制,用于与FPGA、CPLD、ASIC等的接口,以及与一个硬盘驱动器的直接接口

•增强型直接内存访问(EDMA)控制器

–四个传输控制器

–64个独立DMA信道和8个独立QDMA信道

•双端口以太网(10/100/1000 Mbps),带可选交换机

–符合IEEE 802.3(仅限3.3-V I/O)

–MII/RMII/GMII/RGMII媒体独立接口

•片上ARM ROM引导加载程序(RBL)

–管理数据I/O(MDIO)模块

–重置隔离

–IEEE 1588时间戳和工业以太网协议

•带集成PHY的双USB 2.0端口

–USB2.0高速和全速客户端

–USB2.0高速、全速和低速主机或OTG

–支持端点0–15

•一个带有集成PHY的PCI Express 2.0端口

–5.0 GT/s的单通道单端口

–可配置为根复合体或端点

•八个32位通用定时器(定时器1–8)

•一个系统看门狗定时器(WDT0)

•六个可配置UART/IrDA/CIR模块

–带调制解调器控制信号的UART0

–最高支持3.6864 Mbps UART0/1/2

–最高支持12 Mbps UART3/4/5

–SIR、MIR、FIR(4.0 MBAUD)和CIR

•四个串行外围接口(SPI)(最高48 MHz)

–每个具有四个芯片选择

•三个MMC/SD/SDIO串行接口(最高48 MHz)

–三种支持最多1位、4位或8位模式

•双控制器局域网(DCAN)模块

–CAN版本2 A、B部分

•四个内部集成电路(I2C总线)端口

•六个多通道音频串行端口(McASP)

–双十串行器发送和接收

–四个串行化器发送和接收端口

–支持S/PDIF的DIT(所有端口)

•多通道缓冲串行端口(McBSP)

–发送和接收时钟高达48 MHz

–两个时钟区和两个串行数据引脚

–支持TDM、I2S和类似格式

•带集成PHY的串行ATA(SATA)3.0 Gbps控制器

–直接连接到一个硬盘驱动器

–硬件辅助本机命令队列(NCQ),最多32个条目

–支持端口乘法器和基于命令的切换

–一次性或周期性中断生成

•最多128个通用I/O(GPIO)引脚

•一个自旋锁模块,最多128个硬件信号

•一个带有12个邮箱的邮箱模块

•片上ARM ROM引导加载程序(RBL)

•电源、重置和时钟管理

–多个独立的核心电源域

–多个独立的核心电压域

–支持三个操作点(OPP100,

•每个电压域具有集成PHY OPP120、OPP166的双USB 2.0端口

–子系统和外围设备的时钟启用和禁用控制

•32KB嵌入式跟踪缓冲区(ETB)和用于调试的5引脚跟踪接口

•IEEE 1149.1(JTAG)兼容

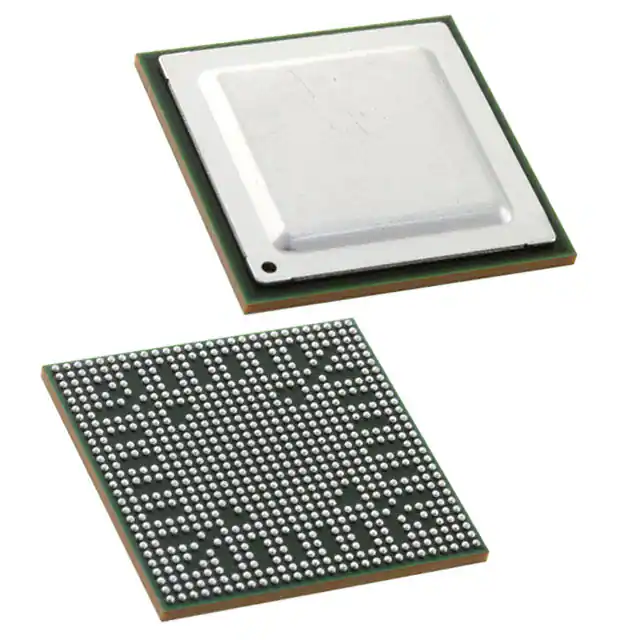

•684引脚无铅BGA封装(CYE后缀),0.8-mm球距,带通孔通道

•45 nm CMOS技术

•1.8 V和3.3 V双电压缓冲器,用于一般I/O

•高清视频会议-Skype®端点

•视频监控DVR、IP网络摄像头

•数字标牌

•媒体播放器和适配器

•移动医学成像

•网络投影仪

•家庭音频和视频设备

TMS320DM814x DaVinci视频处理器是高度集成的可编程平台,可利用DaVinci处理器技术满足以下应用程序的处理需求:

•高清视频会议-Skype端点

•视频监控DVR

•IP网络摄像头

•数字标牌

•媒体播放器和适配器

•移动医学成像

•网络投影仪

•家庭音频和视频设备

该设备使原始设备制造商(OEM)和原始设计制造商(ODM)能够通过完全集成的混合处理器解决方案的最大灵活性,快速将具有强大操作系统支持、丰富用户界面和高处理性能的设备推向市场。该设备还将可编程视频和音频处理与高度集成的外围设备相结合。

TMS320DM814x达芬奇视频处理器还为OEM和ODM提供了新级别的处理器可扩展性和软件重用。OEM或ODM在设计中使用AM387x处理器,并可以制造具有附加功能的类似产品,可以扩展到TI的引脚兼容和可软件兼容的TMS320DM814x处理器。TMS320DM814xDaVinci视频处理器为AM38x的硬件添加了强大的C674x DSP内核以及视频编码器和解码器。此外,使用AM387x或DM814x处理器并发现需要更快的ARM和DSP核心性能的OEM或ODM可以扩展到具有更高核心速度的软件兼容AM389x或TMS320DM816x设备。

可编程性由具有Neon扩展的ARM Cortex-A8 RISC CPU、TI C674x VLIW浮点DSP内核以及高清视频和图像协处理器提供。ARM允许开发人员将控制功能与DSP和协处理器上编程的A/V算法分开,从而降低了系统软件的复杂性。带有Neon浮点扩展的ARM Cortex-A8 32位RISC内核包括:32KB的指令缓存;32KB的数据缓存;512KB的二级缓存;48KB的引导ROM;以及64KB的RAM。

丰富的外围设备集提供了控制外部外围设备和与外部处理器通信的能力。有关每个外围设备的详细信息,请参阅本文档中的相关章节和相关的外围设备参考指南。外围设备包括:

•高清视频处理子系统

•双端口千兆以太网MAC(10/100/1000 Mbps)[以太网交换机],MII/RMI/GMII/RGMII和MDIO接口支持IEEE 1588时间戳和工业以太网协议

•两个USB端口,集成2.0 PHY

•PCIe x1 GEN2兼容接口

•两个10串行器McASP音频串行端口(带DIT模式)

•四个四串口McASP音频串行端口(带DIT模式)

•一个McBSP多通道缓冲串行端口

•六个UART,支持IrDA和CIR

•四个SPI串行接口

•三个MMC/SD/SDIO串行接口

•四个I2C主接口和从接口

•并行摄像头接口(CAM)

•最多128个通用I/O(GPIO)

•八个32位通用计时器

•系统看门狗定时器

•双DDR2和DDR3 SDRAM接口

•灵活的8位或16位异步存储器接口

•两个控制器局域网(DCAN)模块

•旋转锁

•邮箱

•串行硬盘驱动器接口(SATA 300)

TMS320DM814x DaVinci视频处理器还包括一个高清视频和图像协处理器2(HDVICP2)和一个SGX530 3D图形引擎,用于从DSP核心卸载许多视频和图像处理任务,使更多的DSP MIPS可用于普通视频和图像算法。此外,它还为ARM和DSP提供了一套完整的开发工具,包括C编译器、简化编程和调度的DSP汇编优化器,以及用于查看源代码执行的Microsoft®Windows®调试器界面。

特色

- 高性能达芬奇视频处理器

- 高达1GHz ARM Cortex-A8 RISC内核

- 高达750 MHz C674x VLIW DSP

- 最高6000 MIPS和4500 MFLOPS

- 完全软件兼容C67x+、C64x+

- ARM Cortex-A8内核

- ARMv7体系结构

- 有序、双问题、超标量处理器内核

- 霓虹灯多媒体架构

- 支持整数和浮点

- Jazelle RCT执行环境

- ARMv7体系结构

- ARM Cortex-A8内存架构

- 32KB的指令和数据缓存

- 512KB的二级缓存

- 64KB RAM,48KB引导ROM

- TMS320C674x浮点VLIW DSP

- 64个通用寄存器(32位)

- 六个ALU(32-/40位)功能单元

- 支持32位整数、SP(IEEE单精度/32位)和DP(IEEE双精度/64位)浮点

- 每时钟最多支持四个SP加法运算,每两个时钟支持四个DP加法运算

- 每个周期最多支持两个浮点(SP或DP)近似倒数或平方根运算

- 两个乘法功能单元

- 混合精度IEEE浮点乘法最多支持:

- 2 SP x SP→ 每时钟SP

- 2 SP x SP→ DP每两个时钟

- 2个SP x DP→ DP每三个时钟

- 2个DP x DP→ DP每四个时钟

- 定点乘法支持两个32 x 32乘法、四个16 x 16位乘法(包括复数乘法)或每个时钟周期八个8 x 8位乘法

- 混合精度IEEE浮点乘法最多支持:

- C674x两级存储器体系结构

- 32KB带EDC的L1P RAM/缓存

- 32KB的L1D RAM/缓存

- 256KB带ECC的二级统一映射RAM/缓存

- 系统内存管理单元(MMU)

- 将C674x DSP和EDMA TC内存访问映射到系统地址

- 128KB片上存储器控制器(OCMC)RAM

- 成像子系统(ISS)

- 摄像头传感器连接

- Raw(最多16位)和BT.656或BT.1120(8位和16位)的并行连接

- 图像传感器接口(ISIF),用于处理来自摄像机传感器的图像和视频数据

- 调整大小器

- 将图像和视频大小从1/16倍调整为8倍

- 同时生成两个不同的调整大小输出

- 摄像头传感器连接

- 可编程高清视频图像协处理(HDVICP v2)引擎

- 编码、解码、转码操作

- H.264、MPEG-2、VC-1、MPEG-4、SP/ASP、JPEG/MJPEG

- 媒体控制器

- 控制HDVPSS、HDVICP2和ISS

- SGX530 3D图形引擎

- 提供敢达25 MPoly/秒

- 通用可扩展着色器引擎

- Direct3D Mobile、OpenGLES 1.1和2.0、OpenVG 1.0、OpenMax API支持

- 高级几何DMA驱动操作

- 可编程HQ图像消除混叠

- 持久性

- ARM和DSP指令/数据–Little Endian

- 高清视频处理子系统(HDVPSS)

- 两个165 MHz、2信道高清视频捕获模块

- 一个16-/24位输入或双8位SD输入通道

- 一个8-/16-24位输入和一个仅8位输入通道

- 两个165 MHz高清视频显示输出

- 一个16、24或30位输出和一个16或24位输出

- 复合或S-Video模拟输出

- 提供Macrovision支持

- 带集成PHY的数字HDMI 1.3发射机

- 高级视频处理功能,如扫描、格式、速率转换

- 三个图形层和合成器

- 两个165 MHz、2信道高清视频捕获模块

- 双32位DDR2/DDR3 SDRAM接口

- 最高支持DDR2-800和DDR3-1066

- 最多8 x 8个设备,总地址空间为2GB

- 动态内存管理器(DMM)

- 可编程多区存储器映射和交织

- 实现高效的2D块访问

- 支持0°、90°、180°或270°方向的平铺对象和镜像

- 优化交错访问

- 通用内存控制器(GPMC)

- 8位或16位多路复用地址和数据总线

- 512MB的地址空间被划分为最多8个芯片选择

- NOR闪存、NAND闪存(BCH/Hamming错误代码检测)、SRAM和伪SRAM的无胶接口

- GPMC外部的错误定位模块(ELM)为NAND提供最多16位或512字节的硬件ECC

- FPGA、CPLD、ASIC等接口的灵活异步协议控制

- 增强型直接存储器存取(EDMA)控制器

- 四个传输控制器

- 64个独立DMA信道和8个独立QDMA信道

- 双端口以太网(10/100/1000 Mbps),带可选交换机

- 符合IEEE 802.3(仅限3.3-V I/O)

- MII/RMII/GMII/RGMII媒体独立接口

- 管理数据I/O(MDIO)模块

- 重置隔离

- IEEE 1588时间戳和工业以太网协议

- 带集成PHY的双USB 2.0端口

- USB2.0高速和全速客户端

- USB2.0高速、全速和低速主机或OTG

- 支持端点0–15

- 一个带有集成PHY的PCI Express 2.0端口

- 5.0 GT/s的单通道单端口

- 可配置为根复合体或端点

- 八个32位通用定时器(定时器1–8)

- 一个系统看门狗定时器(WDT0)

- 六个可配置UART/IrDA/CIR模块

- 带调制解调器控制信号的UART0

- 最高支持3.6864 Mbps UART0/1/2

- 最高支持12 Mbps UART3/4/5

- SIR、MIR、FIR(4.0 MBAUD)和CIR

- 四个串行外围接口(SPI)(最多

48兆赫)- 每个具有四个芯片选择

- 三个MMC/SD/SDIO串行接口(最多

48兆赫)- 三种支持最多1位、4位或8位模式

- 双控制器局域网(DCAN)模块

- CAN版本2 A、B部分

- 四个集成电路间(I2C总线)端口

- 六个多通道音频串行端口(McASP)

- 双十串行器发送和接收端口

- 四个串行化器发送和接收端口

- 支持DIT的S/PDIF(所有端口)

- 多通道缓冲串行端口(McBSP)

- 发送和接收时钟高达48 MHz

- 两个时钟区和两个串行数据引脚

- 支持TDM、I2S和类似格式

- 带集成PHY的串行ATA(SATA)3.0 Gbps控制器

- 一个硬盘驱动器的直接接口

- 硬件辅助本机命令队列(NCQ),最多32个条目

- 支持端口乘法器和基于命令的切换

- 实时时钟(RTC)

- 一次性或周期性中断生成

- 最多128个通用I/O(GPIO)引脚

- 一个自旋锁模块,最多128个硬件信号

- 一个带有12个邮箱的邮箱模块

- 片上ARM ROM引导加载程序(RBL)

- 电源、重置和时钟管理

- 多个独立核心功率域

- 多个独立的核心电压域

- 每个电压域支持三个操作点(OPP100、OPP120、OPP166)

- 子系统和外围设备的时钟启用和禁用控制

- 32KB的嵌入式跟踪缓冲区(ETB)和

用于调试的5引脚跟踪接口 - IEEE 1149.1(JTAG)兼容

- 684引脚无铅BGA封装(CYE后缀),0.8-mm球间距,采用通孔通道技术,降低PCB成本

- 45纳米CMOS技术

- 1.8和3.3V双电压缓冲器,用于通用I/O