TMS320C64x+DSP(包括TMS320C6474FZUNA2器件)是TMS320C6000 DSP平台中性能最高的多核DSP代。

C6474设备基于德州仪器(TI)开发的第三代高性能高级VelociTI超长指令字(VLIW)架构。

C64x+设备与属于C6000 DSP平台的先前设备的代码向上兼容。

特色

-

- 高性能多核DSP(C6474)

- 指令周期时间:0.83 ns(1.2-GHz设备);1ns(1-GHz设备);1.18 ns(850 MHz设备)

- 时钟频率:1 GHz至1.2 GHz(1.2 GHz设备);1GHz(1-GHz设备);850 MHz(850 MHz设备)

- 商业温度和扩展温度

- 3个TMS320C64x+DSP内核;用于CDMA处理的六个RSA(每个核心2个)

- 增强的VCP2/TCP2

- 帧同步接口

- 16-/32位DDR2-667内存控制器

- EDMA3控制器

- 天线接口

- 两个1x串行RapidIO链路,符合v1.2

- 一条1.8V内部集成电路(I2C)总线

- 两个1.8-V McBSP

- 1000 Mbps以太网MAC(EMAC)

- 六个64位通用定时器

- 16个通用I/O(GPIO)引脚

- 非UMTS系统的内部信号量模块

- 系统PLL和PLL控制器/DDR PLL和锁相环控制器,专用于DDR2内存控制器

- 高性能多核DSP(C6474)

- 指令周期时间:

- 1.2GHz设备:1.0-ns至0.83-ns

- 1-GHz设备:1-ns

- 850 MHz设备:1.18 ns

- 时钟频率:

- 1.2-GHz设备:1-GHz至1.2-GHz

- 1-GHz设备:1-GHz

- 850 MHz设备:850 MHz

- 八个32位指令/周期

- 商业温度:

- 1.2-GHz设备:0°C至95°C

- 1-GHz设备:0°C至100°C

- 850-MHZ和1-GHz设备:0°C至100°C

- 扩展温度:

- 1.2GHz设备:-40°C至95°C

- 1-GHz设备:-40°C至100°C

- 指令周期时间:

- 3个TMS320C64x+DSP内核

- 专用SPLOOP说明

- 精简指令(16位)

- 异常处理

- TMS320C64x+Megamodule L1/L2内存结构

- 256 K位(32 K字节)L1P程序缓存[直接映射]

- 256 K位(32 K字节)L1D数据缓存[2路集合关联]

- 512 K位(64 K字节)L3 ROM

- 增强的VCP2

- 支持超过694 7.95-Kbps的AMR

- 增强型Turbo解码器协处理器(TCP2)

- 最多支持8个2-Mbps 3 GPP(6次迭代)

- 无尽:小无尽,大无尽

- 帧同步接口

- 内部子系统、外部设备/系统之间的时间对齐

- OBSAI RP1兼容帧突发数据

- 非RP1和非UMTS系统的备用接口

- 16-/32位DDR2-667内存控制器

- EDMA3控制器(64个独立信道)

- 天线接口

- 6个可配置链路(全双工)

- 支持OBSAI RP3协议,v1.0:768 Mbps,1.536-,3.072-Gbps链路速率

- 支持CPRI协议V2.0:614.4-Mbps、1.2288-、2.4576-Gbps链路速率

- 时钟输入独立或与CPU共享(可在启动时选择)

- 两个1x串行RapidIO链路,符合v1.2

- 1.25-、2.5-、3.125-Gbps链路速率

- 消息传递和DirectIO支持

- 错误管理扩展和拥塞控制

- 一条1.8V内部集成电路(I2C)总线

- 两个1.8-V McBSP

- 1000 Mbps以太网MAC(EMAC)

- 符合IEEE 802.3

- 支持SGMII,v1.8兼容

- 8个独立发射(TX)和8个独立接收(RX)信道

- 六个64位通用定时器

- 最多可配置12个32位定时器

- 可在看门狗定时器模式下配置

- 16个通用I/O(GPIO)引脚

- 内部信号量模块

- 控制共享资源访问的软件方法

- 32通用信号量资源

- 系统PLL和PLL控制器

- DDR PLL和PLL控制器,专用于DDR2内存控制器

- IEEE-1149.1和IEEE-1149.6(JTAG)边界扫描兼容

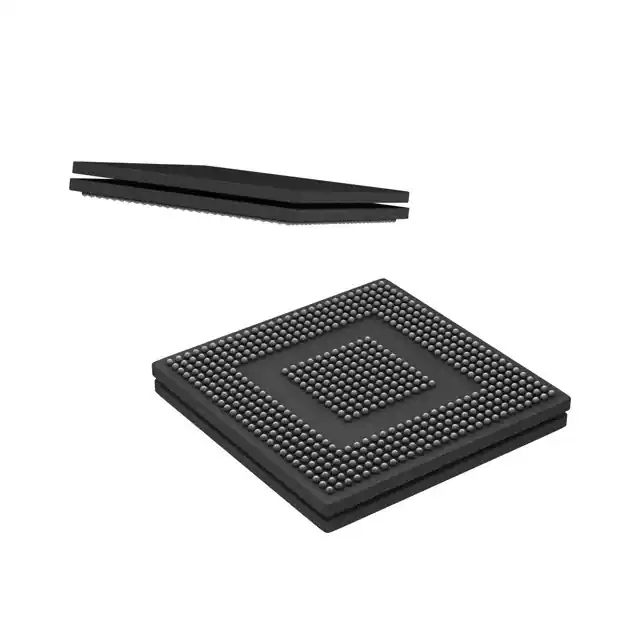

- 561销球栅格阵列(BGA)封装(CUN、GUN或ZUN后缀),0.8-mm球间距

- 0.065μm/7级铜金属工艺(CMOS)

- SmartReflex 0级已启用-0.9V至1.2V自适应核心电压

- 1.8伏、1.1伏I/O