说明:

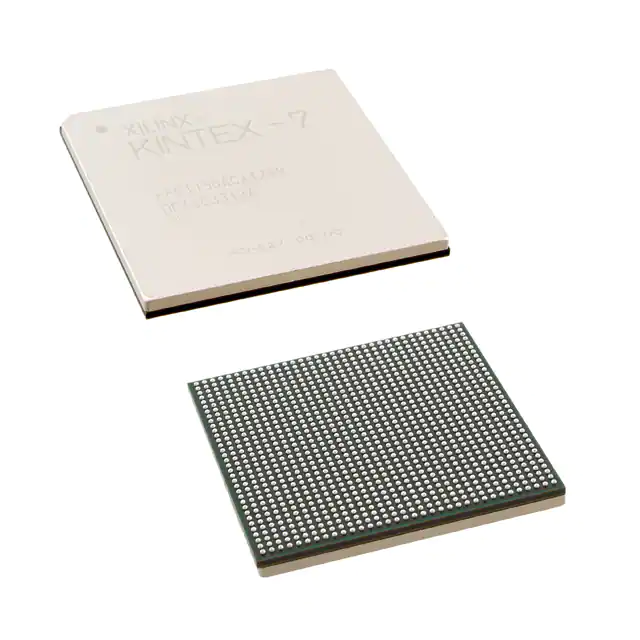

Virtex®-6 FPGA是目标设计平台的可编程硅基础,提供集成的软件和硬件组件,使设计人员能够在开发周期开始时就专注于创新。使用第三代ASMBL™ Virtex-6系列包含多个不同的子系列。本概述涵盖LXT、SXT和HXT子系列中的设备。每个子系列包含不同比例的功能,以最有效地满足各种高级逻辑设计的需求。除了高性能逻辑结构外,Virtex-6 FPGA还包含许多内置系统级块。这些特性允许逻辑设计人员在基于FPGA的系统中构建最高级别的性能和功能。Virtex-6 FPGA基于40纳米最先进的铜工艺技术,是定制ASIC技术的可编程替代品。Virtex-6 FPGA为满足高性能逻辑设计人员、高性能DSP设计人员和高性能嵌入式系统设计人员的需求提供了最佳解决方案,具有前所未有的逻辑、DSP、连接和软微处理器功能。

Virtex-6 FPGA概述

特征:

•三个子系列:

•Virtex-6 LXT FPGA:具有高级串行连接的高性能逻辑

•Virtex-6 SXT FPGA:具有高级串行连接的最高信号处理能力

•Virtex-6 HXT FPGA:最高带宽串行连接

•子系列间的兼容性

•LXT和SXT设备在同一封装中兼容

•高级、高性能FPGA逻辑

•真正的6输入查找表(LUT)技术

•双LUT5(5输入LUT)选项

•LUT/双触发器对,适用于需要丰富寄存器混合的应用

•提高布线效率

•每个6输入LUT的64位(或两个32位)分布式LUT RAM选项

•SRL32/双SRL16,带注册输出选项

•强大的混合模式时钟管理器(MMCM)

•MMCM模块提供零延迟缓冲、频率合成、时钟相移、输入抖动滤波和相位匹配时钟分割

•36 Kb块RAM/FIFO

•双端口RAM块

•可编程-双端口宽度高达36位-简单的双端口宽度达72位

•增强的可编程FIFO逻辑

•内置可选纠错电路

•可选择将每个块用作两个独立的18 Kb块

•高性能并行SelectIO™ 技术

•1.2至2.5V I/O操作

•使用ChipSync的源同步接口™ 技术

•数字控制阻抗(DCI)有源终端

•灵活的细粒度I/O银行

•高速存储器接口支持,具有集成的写入均衡功能

•高级DSP48E1芯片

•25 x 18,二进制补码乘法器/累加器

•可选管道

•新的可选前置加法器,以帮助过滤应用

•可选位逻辑功能

•专用级联连接

•灵活的配置选项

•SPI和并行闪存接口

•具有专用回退重新配置逻辑的多位流支持

•自动总线宽度检测

•所有设备上的系统监控功能

•片内/片外热和电源电压监测

•JTAG访问所有监测数量

•PCI Express®设计的集成接口块

•符合PCI Express基本规范2.0

•GTX收发器支持第1代(2.5 Gb/s)和第2代(5 Gb/s)

•支持端点和根端口

•每个街区支持x1、x2、x4或x8车道

•GTX收发器:高达6.6 Gb/s

•FPGA逻辑中的过采样支持低于480 Mb/s的数据速率。

•GTH收发器:2.488 Gb/s至超过11 Gb/s

•集成10/100/1000 Mb/s以太网MAC块

•使用GTX收发器支持1000BASE-X PCS/PMA和SGMII

•使用SelectIO技术资源支持MII、GMII和RGMII

•提供2500Mb/s支持

•40 nm铜CMOS工艺技术

•1.0V铁芯电压(仅限-1、-2、-3速度等级)

•低功率0.9V核心电压选项(仅限-1L速度等级)

•提供标准或无铅封装选项的高信号完整性倒装芯片封装

特色

- 三个子家族:

- Virtex-6 LXT FPGA:具有高级串行连接的高性能逻辑

- Virtex-6 SXT FPGA:具有高级串行连接的最高信号处理能力

- Virtex-6 HXT FPGA:最高带宽串行连接

- 子族间的兼容性

- LXT和SXT设备在同一封装中兼容

- 先进、高性能FPGA逻辑

- 真实6输入查找表(LUT)技术

- 双LUT5(5输入LUT)选项

- LUT/双触发器对,适用于需要丰富寄存器混合的应用

- 提高了路由效率

- 每6输入LUT 64位(或两个32位)分布式LUT RAM选项

- SRL32/双SRL16,带注册输出选项

- 强大的混合模式时钟管理器(MMCM)

- MMCM模块提供零延迟缓冲、频率合成、时钟相移、输入抖动滤波和相位匹配时钟分割

- 36 Kb块RAM/FIFO

- 双端口RAM块

- 可编程的

- 双端口宽度高达36位

- 简单的双端口宽度高达72位

- 增强型可编程FIFO逻辑

- 内置可选纠错电路

- 可选地,将每个块用作两个独立的18 Kb块

- 高性能并行SelectIO™ 技术

- 1.2至2.5V I/O操作

- 使用ChipSync的源同步接口™ 技术

- 数字控制阻抗(DCI)有源终端

- 灵活的细粒度I/O存储

- 具有集成写入均衡功能的高速内存接口支持

- 高级DSP48E1切片

- 25 x 18,二进制补码乘法器/累加器

- 可选管道

- 新的可选前置加法器,以帮助过滤应用

- 可选的按位逻辑功能

- 专用级联连接

- 灵活的配置选项

- SPI和并行闪存接口

- 具有专用回退重新配置逻辑的多位流支持

- 自动母线宽度检测

- 所有设备上的系统监视器功能

- 片内/片外热和电源电压监测

- JTAG访问所有监测数量

- PCI Express®设计的集成接口块

- 符合PCI Express基本规范2.0

- GTX收发器支持第1代(2.5 Gb/s)和第2代(5 Gb/s)

- 支持端点和根端口

- 每个块的X1、x2、x4或x8车道支持

- GTX收发器:最高6.6 Gb/s

- FPGA逻辑中的过采样支持低于480Mb/s的数据速率。

- GTH收发器:2.488 Gb/s至超过11 Gb/s

- 集成10/100/1000 Mb/s以太网MAC块

- 使用GTX收发器支持1000BASE-X PCS/PMA和SGMII

- 使用SelectIO技术资源支持MII、GMII和RGMII

- 提供2500Mb/s支持

- 40nm铜CMOS工艺技术

- 1.0V铁芯电压(仅限-1、-2、-3速度等级)

- 低功率0.9V核心电压选项(仅限-1L速度等级)

- 高信号完整性倒装芯片封装提供标准或无铅封装选项