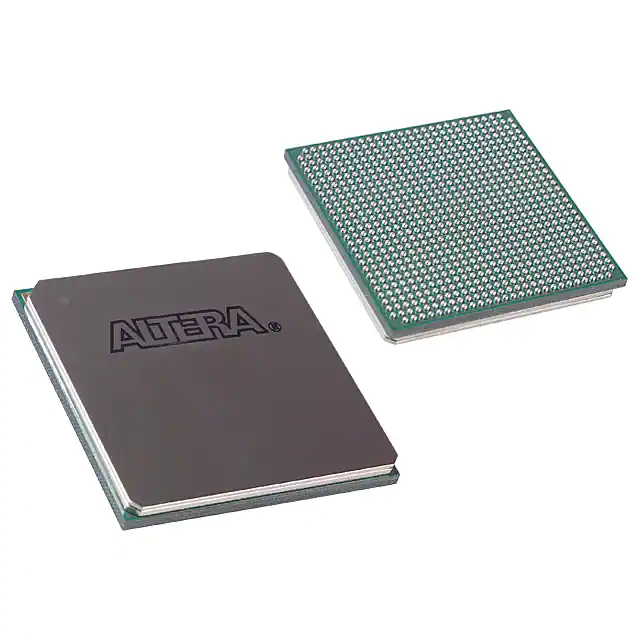

特征

■ Altera®ACEX®1K、APEX的单芯片配置解决方案™ 20K(包括APEX 20K、APEX 20KC和APEX 20KE)、APEX II、Arria®GX、Cyclone®、Cyclone II、FLEX®10K(包括FLEX 10KE和FLEX 10KA)、Mercury™, Stratix®II和Stratix II GX设备

■ 包含用于配置数据存储的4、8和16 Mbit闪存

■ 片上解压缩功能几乎使有效配置密度翻倍

■ 标准闪存管芯和控制器管芯组合成单个堆叠芯片封装

■ 外部闪存接口支持并行编程闪存和外部处理器访问未使用的内存部分

■ 通过外部闪存接口实现闪存块/扇区保护功能

■ EPC16和EPC4设备支持

■ 页面模式支持远程和本地重新配置,整个系统最多有八种配置

■ 与Stratix系列远程系统配置功能兼容

■ 支持字节宽配置模式快速无源并行(FPP);每个DCLK周期8位数据输出

■ 支持Altera FPGA的真正n位并发配置(n=1、2、4和8)

■ 引脚可选2毫秒或100毫秒通电复位(POR)时间

■ 配置时钟支持可编程输入源和频率合成

■ 支持多个配置时钟源(内部振荡器和外部时钟输入引脚)

■ 频率高达100 MHz的外部时钟源

■ 内部振荡器默认为10MHz;可编程用于33、50和66 MHz的较高频率

■ 通过用户可编程分频计数器支持时钟合成

■ 可提供100针塑料方形扁平封装(PQFP)和88针Ultra FineLine BGA®(UFBGA)封装

■ 100引脚PQFP封装中支持的所有设备之间的垂直迁移

■ 3.3 V电源电压(核心和I/O)

■ 硬件符合IEEE标准1532系统可编程性(ISP)规范

■ 通过Jam标准测试和编程语言(STAPL)支持ISP

■ 支持JTAG边界扫描

■ nINIT_CONF引脚允许专用JTAG指令启动FPGA配置

■ nINIT_CONF上的内部上拉电阻器始终启用

■ nCS和OE引脚上的用户可编程弱内部上拉电阻器

■ 外部闪存接口地址和控制线上的内部弱上拉电阻器,数据线上的总线保持

■ 待机模式,功耗降低

功能描述

Altera增强配置设备是一种用于高密度FPGA的单设备、高速、高级配置解决方案。增强型配置设备的核心分为两个主要模块:配置控制器和闪存。闪存用于存储由一个或多个Altera FPGA组成的系统的配置数据。闪存的未使用部分可用于存储处理器代码或数据,这些代码或数据可在FPGA配置完成后通过外部闪存接口访问。表1–1总结了Altera配置设备的特点及其所占的配置空间。

特色

■ 主要设备特点:

● TriMatrix内存由三个RAM块大小组成,可实现真正的双端口内存和先进先出(FIFO)缓冲区,性能高达550 MHz

● 最多16个全球时钟网络,每个设备区域最多32个区域时钟网络

● 高速DSP模块提供乘法器(最高450 MHz)、乘法累加函数和有限脉冲响应(FIR)滤波器的专用实现

● 每个设备最多四个增强型PLL提供扩展频谱、可编程带宽、时钟切换、实时PLL重新配置以及高级乘法和相移

● 支持多种单端和差分I/O标准