莱迪思半导体iCE65可编程逻辑系列专门设计用于提供任何可比CPLD或FPGA器件的最低静态和动态功耗。iCE65设备专为成本敏感的高容量应用而设计,并提供片上非易失性配置存储器(NVCM),可为特定应用定制。iCE65设备可以根据存储在外部商品SPI串行闪存PROM中的配置映像进行自我配置,也可以通过类似SPI的串行端口从外部处理器下载。表1中突出显示的三个iCE65组件提供大约1K到接近8K的逻辑单元和触发器,同时消耗相当可编程逻辑设备的一小部分功率。每个iCE65设备包括16到32个RAM块,每个块具有4K位存储,用于片上数据存储和数据缓冲。如图1所示,每个iCE65设备由四个主要架构元素组成。

可编程逻辑块(PLB)阵列

每个PLB包含八个逻辑单元(LC);每个逻辑单元包括…

一种快速的四输入查找表(LUT4),能够实现多达四个输入的任何组合逻辑功能,而不考虑复杂性

带有可选时钟启用和设置/复位控制的“D”型触发器

快速进位逻辑,用于加速加法器、减法器、比较器和计数器等算术功能。

所有八个逻辑单元共享公共时钟输入、极性控制、时钟启用输入和PLB的可选设置/重置控制输入

双端口,4Kbit RAM块(RAM4K)

256x16默认配置;使用可编程逻辑资源选择数据宽度

同时读写访问;适用于FIFO存储器和数据缓冲应用

配置期间可预加载RAM内容

四个具有独立电源电压的I/O组,每个组具有多个可编程输入/输出(PIO)块

所有存储体均支持LVCMOS I/O标准和LVDS输出

I/O Bank 3支持额外的SSTL、MDDR、LVDS和SubLVDS I/O标准

模块之间的可编程互连

所有可编程逻辑功能之间的灵活连接

八个专用的低偏斜、高扇出时钟分配网络

特色

第一个高密度、超低功耗单片SRAM mobileFPGA系列,专为手持应用和长电池寿命而设计

静态模式下为12µA

两种功率/速度选项–L:低功率–T:高速

高达256 MHz的内部性能

可从各种来源和方法重新编程

类似处理器的模式从外部、商品SPI串行闪存PROM自我配置

由处理器使用类似SPI的串行接口下载,仅需20µs

在系统可编程、类似ASIC的模式下,从安全、内部非易失性配置存储器(NVCM)加载

适合批量生产

卓越的设计和知识产权保护;无暴露数据

经验证的高容量65nm低功耗CMOS技术

低泄漏,µW静态功率

更低的核心电压,最低的动态功率

灵活的可编程逻辑和可编程互连结构

超过7600个查找表(LUT4)和触发器

低功耗逻辑和互连

灵活的I/O引脚可简化系统接口

多达222个可编程I/O引脚

四个独立供电的I/O组;支持3.3V、2.5V、1.8V和1.5V电压标准

LVCMOS、MDDR、LVDS和SubLVDS I/O标准

丰富、快速的片上4Kbit RAM块

低成本、节省空间的包装选项

已知良好模具(KGD)选项可用

完整iCEcube™ 开发系统

Windows®和Linux®支持

VHDL和Verilog逻辑综合

放置和布线软件

设计和IP核心库

低成本iCEman65开发板

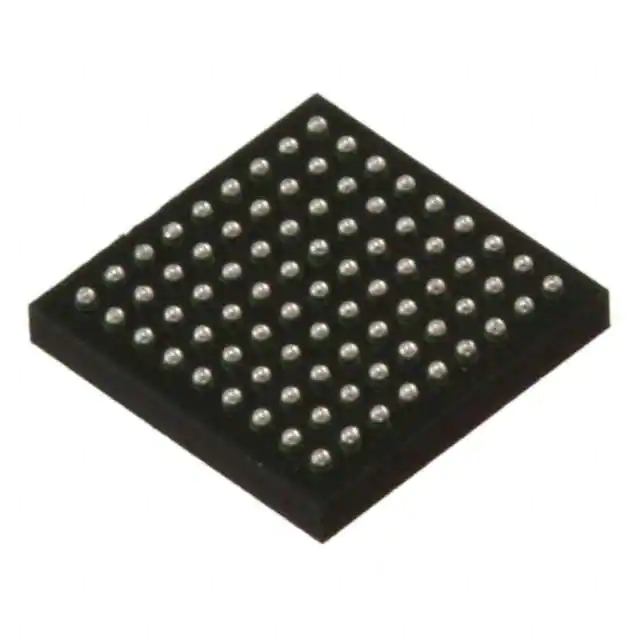

(图片:引出线)