LatticeECP/EC系列FPGA器件经过优化,以低成本提供主流FPGA功能。为了实现最大性能和价值,LatticeECP(EConomy Plus)FPGA概念将高效的FPGA结构与高速专用功能相结合。莱迪思第一个实现这种方法的家族是LatticeECP DSP(EConomy Plus DSP)家族,提供专用的高性能DSP芯片块。LatticeEC公司™ (EConomy)系列支持LatticeECP设备的所有通用功能,无需专用功能块,以实现成本更低的解决方案。

LatticeECP/EC FPGA结构从一开始就以低成本设计,包含所有关键的FPGA元素:基于LUT的逻辑、分布式和嵌入式存储器、PLL和对主流I/O的支持。还包括专用DDR内存接口逻辑,以支持这种在成本敏感应用中日益流行的内存。

莱迪思的ispLEVER®设计工具允许使用LatticeECP/EC系列FPGA设备高效地实现大型复杂设计。LatticeECP/EC的合成库支持可用于流行的逻辑合成工具。ispLEVER工具使用合成工具输出及其楼层规划工具的约束,将设计放置在LatticeECP/EC设备中并进行布线。ispLEVER工具从路由中提取定时,并将其反注释到设计中以进行定时验证。

莱迪思提供许多预先设计的IP(知识产权)ispLeverCORE™ LatticeECP/EC系列的模块。通过使用这些IP作为标准化块,设计师可以自由地专注于其设计的独特方面,从而提高生产力。

特色

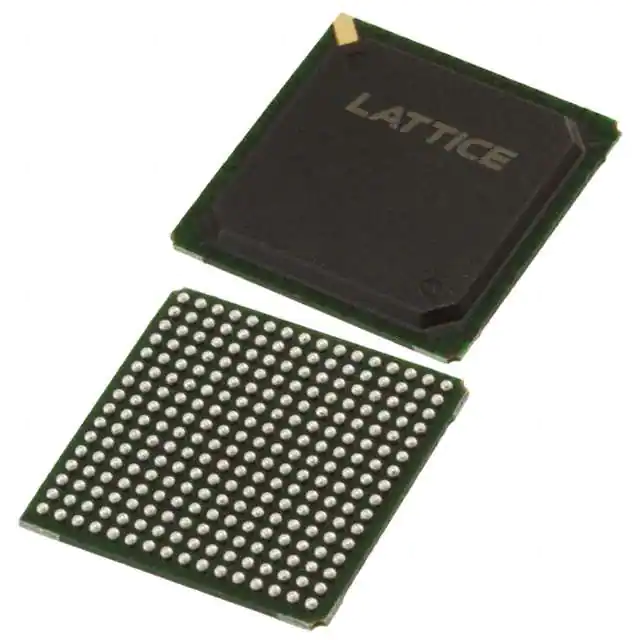

■ 广泛的密度和包装选项

•1.5K至41K LUT4

•65至576个I/O

•支持密度迁移

■ 系统DSP™ 块(LatticeECP™ 版本)

•高性能乘法和累加

•4至10个街区

−4至10个36x36乘数或

–16至40个18x18乘法器或

−32至80个9x9乘法器

■ 嵌入式和分布式内存

•18 Kbits至645 Kbits sysMEM™ 嵌入式块RAM(EBR)

•高达163 Kbits的分布式RAM

•灵活的内存资源:

−分布式和块内存

■ 灵活的I/O缓冲区

•可编程系统IO™ 缓冲区支持多种接口:

−LVCMOS 3.3/2.5/1.8/1.5/1.2

−LVTTL−SSTL 3/2 I级、II级、SSTL18 I级

−HSTL 18 I、II、III级,HSTL15 I、III级

−PCI

−LVDS、总线LVDS、LVPECL、RSDS

■ 专用DDR内存支持

•实现高达DDR400(200MHz)的接口

■ 系统时钟™ 公共图书馆

•每个设备最多4个模拟PLL

•时钟倍增、分频和移相

■ 系统级支持

•IEEE标准1149.1边界扫描,外加ispTRACY™ 内部逻辑分析仪能力

•SPI启动闪存接口

•1.2V电源

■ 低成本FPGA

•针对主流应用程序优化的功能

•低成本TQFP和PQFP包装