微控制器的e200z4主机处理器核心基于Power Architecture®技术,专为嵌入式应用而设计。除了Power Architecture技术之外,该内核还支持数字信号处理(DSP)指令。

SPC5644AF0MMG3具有两级内存层次结构,由8 KB的指令缓存、192 KB的片上SRAM和4 MB的内部闪存支持。SPC5644AF0MMG3包括一个外部总线接口,以及一个仅在使用Freescale VertiCal校准系统时才可访问的校准总线。

该文件描述了SPC5644AF0MMG3的功能,并强调了该设备的重要电气和物理特性。

特色

•150 MHz e200z4电源架构核心

-可变长度指令编码(VLE)

-具有2个执行单元的超标量体系结构

-每个周期最多2条整数或浮点指令

-每个周期最多4次乘法和累加运算

•记忆组织

-4 MB片上闪存,带ECC和读写(RWW)

-192 KB片上SRAM,具有待机功能(32 KB)和ECC

-8 KB指令缓存(带行锁定),可配置为2路或4路

-14+3 KB eTPU代码和数据RAM

-5 x 4交叉开关(XBAR)

-24入口MMU

-带从端口和主端口的外部总线接口(EBI)

•故障安全保护

-16项内存保护单元(MPU)

-具有3个子模块的CRC单元

-接头温度传感器

•中断

-可配置中断控制器(带NMI)

-64通道DMA

•串行通道

-3 x eSCI

-3 x DSPI(其中2个支持下游微秒信道[MSC])

-3个FlexCAN,每个具有64条消息

-1个FlexRay模块(V2.1),最高10 Mbit/s,双通道或单通道,128个消息对象和ECC

•1 x eMIOS:24个统一频道

•1 x eTPU2(第二代eTPU)

-32个标准通道

-1个反应模块(6个通道,每个通道三个输出)

•2个增强型排队模数转换器(eQADC)

-40个12位输入通道(在2个ADC上复用);可扩展至56个信道,带外部多路复用器

-6个命令队列

-触发器和DMA支持

-688 ns最小转换时间

•带引导辅助模块(BAM)的片上CAN/SCI/FlexRay引导加载器

•Nexus公司

-e200z4核心的3+级

-eTPU等级1

•JTAG(5针)

•开发触发信号量(DTS)

-信号量寄存器(32位)和标识寄存器

-用作触发数据采集协议的一部分

-EVTO引脚用于与外部工具通信

•时钟生成

-片上4–40 MHz主振荡器

-片上FMPLL(调频锁相环)

•多达120条通用I/O线

-可单独编程为输入、输出或特殊功能

-可编程阈值(滞后)

•省电模式:慢速、停止和待机模式

•灵活的供应方案

-带外部镇流器的5V单电源

-多个外部电源:5V、3.3V和1.2V

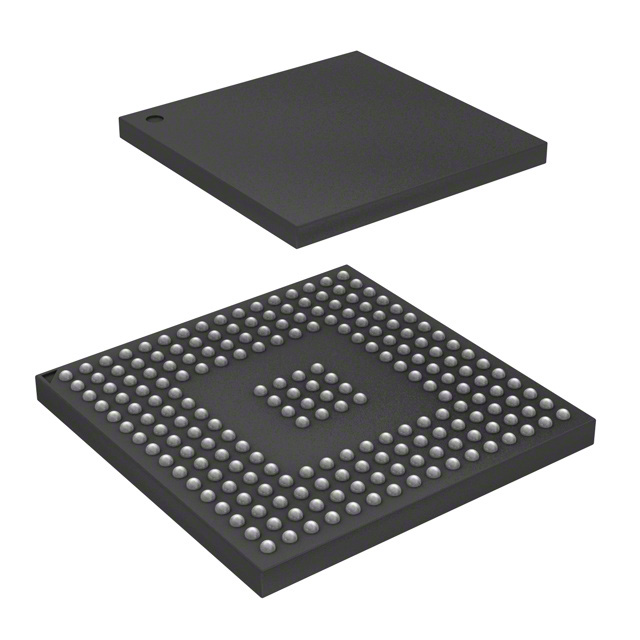

•包装

-176升/分钟

-208地图

-324泰布加

496针CSP(仅限校准工具)