HMC7044LP10BE是一种高性能、双环路、整数N抖动衰减器,能够为具有并行或串行(JESD204B/JESD204C型)接口的高速数据转换器执行基准选择和超低相位噪声频率的生成。HMC7044LP10BE具有两个整数模式PLL和重叠的片上VCO,它们可以分别在2.5 GHz和3 GHz左右的宽调谐范围内进行SPI选择。该设备旨在满足GSM和LTE基站设计的要求,并提供广泛的时钟管理和分配功能,以简化基带和射频卡时钟树设计。HMC7044LP10BE提供14个低噪声和可配置输出,在与许多不同组件(包括数据转换器、现场可编程门阵列(FPGA)和混频器本地振荡器(LO))接口时提供灵活性。

HMC7044LP10BE的DCLK和SYSREF时钟输出可配置为支持信号标准,如CML、LVDS、LVPECL和LVCMOS,以及不同的偏置设置,以抵消不同的板插入损耗。

特色

- 超低均方根抖动:2457.6 MHz时,典型值为44 fs(12 kHz至20 MHz)

- 噪声下限:−156 dBc/Hz,2457.6 MHz

- 低相位噪声:−141.7 dBc/Hz,800 kHz,983.04 MHz输出

- PLL2最多可提供14个LVDS、LVPECL或CML型设备时钟(DCLK)

- 最大CLKOUTx/CLKOUTx和SCLKOUTx/SCLKOUTx频率高达3200 MHz

- JESD204B/JESD204C兼容系统参考(SYSREF)脉冲

- 25 ps模拟和½VCO周期数字延迟,可在14个时钟输出通道中的每个通道上独立编程

- SPI可编程相位噪声与功耗

- SYSREF有效中断以简化JESD204B/JESD204C同步

- 窄带双核VCO

- 最多2个缓冲压控振荡器(VCXO)输出

- LVDS、LVPECL、CMOS和CML模式下最多4个输入时钟

- 保持输出频率的频率保持模式

- 信号丢失(LOS)检测和无中断参考切换

- 4×GPIO警报/状态指示器,用于确定系统的运行状况

- 外部VCO输入,最高支持6000 MHz

- 实现卓越PSRR的车载稳压器

- 68引线,10 mm×10 mm LFCSP封装

应用

- JESD204B/JESD204C时钟生成

- 蜂窝基础设施(多载波GSM、LTE、W-CDMA)

- 数据转换器计时

- 微波基带卡

- 相控阵参考分布

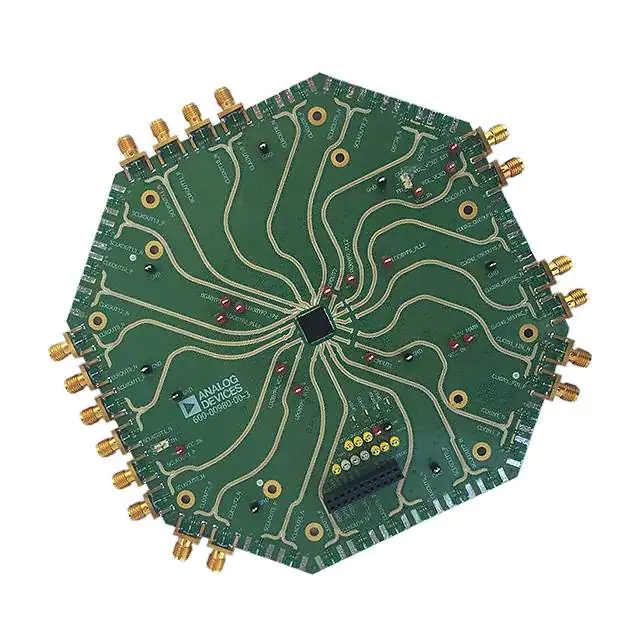

(图片:引出线)