AD9515/PCBZ采用双输出时钟分配IC,其设计强调低抖动和相位噪声,以最大化数据转换器性能。具有苛刻相位噪声和抖动要求的其他应用也受益于此部分。

有两个独立的时钟输出。一个输出是LVPECL,而另一个输出可以设置为LVDS或CMOS电平。LVPECL输出工作在1.6 GHz。另一个输出在LVDS模式下工作至800MHz,在CMOS模式下工作到250MHz。

每个输出都有一个可编程除法器,可以设置为除以1到32范围内的一组选定整数。一个时钟输出相对于另一时钟输出的相位可以通过用作粗略定时调整的分频器相位选择功能来设置。

LVDS/CMOS输出具有一个延迟元件,具有三个可选择的满刻度延迟值(1.5 ns、5 ns和10 ns),每个值具有16个微调步骤。

AD9515/PCBZ不需要外部控制器进行操作或设置。该设备通过11个引脚(S0至S10)使用4级逻辑进行编程。编程引脚内部偏置至⅓ VREF引脚提供⅔ VS(3.3V)和GND(0V)提供另外两个逻辑电平。

AD9515/PCBZ非常适合数据转换器时钟应用,其中通过对具有亚皮秒抖动的信号进行编码来实现最大转换器性能。

AD9515/PCBZ采用32引脚LFCSP,由单个3.3V电源供电。温度范围为−40°C至+85°C。

特色

- 1.6 GHz差分时钟输入

- 2个可编程分频器,范围从1到32,相位选择用于输出到输出的粗延迟调整

- 1.6 GHz LVPECL时钟输出VPECL相加输出抖动225 fs rms

- 800 MHz/250 MHz LVDS/CMOS时钟输出VDS/CMOS加法输出抖动300 fs rms/290 fs rms时间延迟高达10 ns

- 配置有4级逻辑引脚的设备

- 节省空间,32导联LFCSP

应用

- 低抖动、低相位噪声时钟分布

- 时钟高速ADC、DAC、DDS、DDC、DUC、MxFE

- 高性能无线收发器

- 高性能仪表

- 宽带基础设施

- 吃了

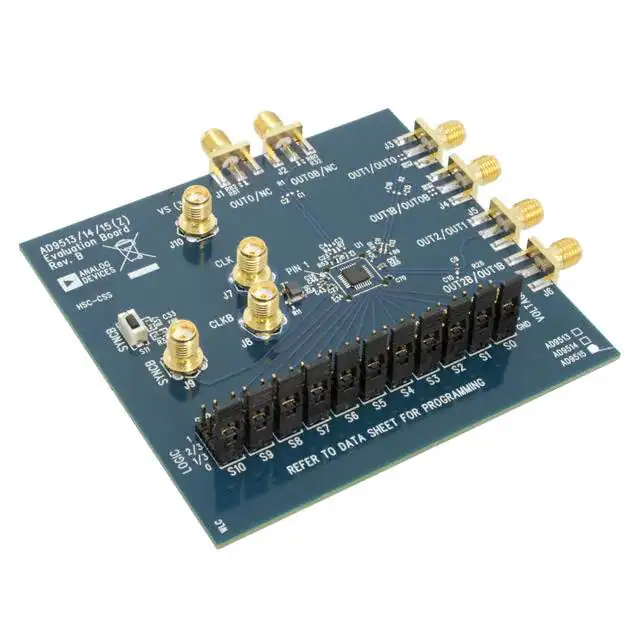

(图片:引出线)