CDCE421AEVM是一款高性能、低相位噪声时钟发生器。它有两个全集成、低噪声、基于LC的压控振荡器(VCO),工作在1.750-GHz至2.350-GHz频率范围内。它还具有集成晶体振荡器,该振荡器与外部AT切割晶体一起工作,为基于锁相环(PLL)的频率合成器产生稳定的频率基准。

输出频率(fOUT)与输入晶体的频率(fXTAL)成比例。预分频器、反馈分频器、输出分频器和VCO选择设置相对于fXTAL的输出频率。

在CDCE421A中,反馈分频器相对于预分频器设置被自动设置。如图所示,预分频器和反馈分频器的乘积应在60和64之间,以保持稳定的控制回路。

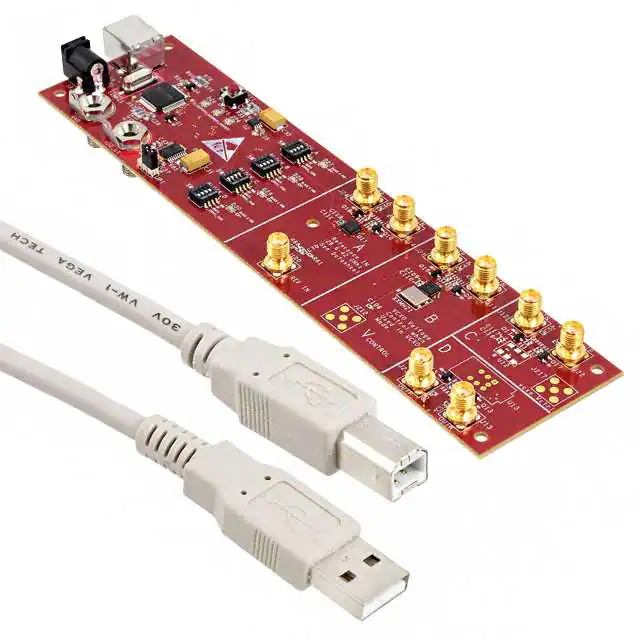

CDCE421AEVM支持一个差动LVDS时钟输出或一个差动LVPECL输出。所有设备设置均可通过专有的简单串行接口(SSI)进行编程。

该设备在用于LVPECL和LVDS输出的3.3V电源环境中工作,其特点是在-40°C至+85°C的温度范围内工作。CDCE421AEVM采用QFN-244-mm×4-mm封装。

CDCE421用户:CDCE421AEVM为CDCE421提供了几个设备增强功能。

特色

- 用于LVPECL或LVDS操作的3.3 V单电源

- 结合晶体振荡器电路和集成频率合成器的高性能时钟乘法器

- 低输出抖动:380 fs RMS典型值(从10 kHz到20 MHz)

- 高频低相位噪声(708 MHz LVPECL):

- 通常,载波频率为10 kHz时为-109 dBc/Hz,频率为10 MHz时为-146 dBc/Hz

- 支持27.35 MHz至38.33 MHz的晶体或LVCMOS输入频率

- 输出频率范围从10.9 MHz到766.7 MHz,从875.2 MHz到1175 MHz

- 低压差分信号(LVDS)输出,100-差分片外终端,10.9MHz至400MHz频率范围

- 差分低压正发射极耦合逻辑(LVPECL)输出,10.9MHz至1.175-GHz频率范围

- 两个全集成压控振荡器(VCO)支持宽输出频率范围

- 全集成可编程环路滤波器

- 3.3 V时的典型功耗:

- LVDS模式下274 mW

- LVPECL模式下250 mW

- 芯片启用控制引脚

- 简单的串行接口允许在制造后编程

- 集成片上非易失性存储器(EEPROM)在不施加高压的情况下存储设置

- 4毫米×4毫米QFN-24封装

- ESD保护超过2 kV(HBM)

- 工业温度范围:-40°C至+85°C

- 应用

- 低成本、高频晶体振荡器