AD9576/PCBZ提供多输出时钟发生器功能,通过监测和自动切换冗余晶体(XTAL)输入,在频率公差范围内提供延长的操作寿命,同时最小化切换、感应瞬变。分数N PLL设计基于股份有限公司模拟设备公司(Analog Devices,Inc.)的高性能、低抖动频率合成器组合,以最大限度地提高网络性能,而整数N PLL提供用作CPU和现场可编程门阵列(FPGA)参考时钟的通用时钟。

AD9576/PCBZ使用引脚捆扎在其11个输出时钟的多种通电就绪配置中进行选择,这只需要将外部上拉或下拉电阻器连接到适当的引脚程序读取器引脚(PPRx)。这些引脚提供对内部分频器的控制,以建立期望的频率转换、时钟输出功能和输入参考功能。这些参数也可以通过串行端口接口(SPI)手动配置。

AD9576/PCBZ封装在64引线、9 mm×9 mm LFCSP中,仅需单个2.5 V或3.3 V电源。工作温度范围为−40°C至+85°C。

每个OUTx输出是差分的,包含两个引脚:OUTx和OUTx。为简单起见,术语OUTx是指包含这两个引脚的功能输出块。。

特色

- 单、低相位噪声、全集成VCO/分数N PLL核心

- VCO范围:2375 MHz至2725 MHz

- 集成环路滤波器(需要单个外部电容器)

- 2个差分、XTAL或单端参考输入

- 参考监控能力

- 自动冗余XTAL切换

- 最小瞬时、平滑切换

- 典型RMS抖动

- <0.3 ps(12 kHz至20 MHz),整数N转换

- <0.5 ps(12 kHz至20 MHz),分数N转换

- 输入频率

- 8 kHz、1.544 MHz、2.048 MHz和10 MHz至325 MHz

- 通过引脚捆扎(PPRx)预设频率转换

- 使用25 MHz输入参考

- 24.576 MHz、25 MHz、33.33 MHz、50 MHz、70.656 MHz、100 MHz、125 MHz、148.5 MHz、156.25 MHz、161.1328 MHz、312.5 MHz、322.256 MHz、625 MHz或644.5313 MHz

- 使用19.44 MHz输入参考

- 50 MHz、100 MHz、125 MHz、156.25 MHz、161.1328 MHz或644.5313 MHz

- 使用30.72 MHz输入参考

- 25 MHz、50 MHz、100 MHz、125 MHz或156.25 MHz

- 使用25 MHz输入参考

- 单个、通用、完全集成的VCO/整数-N PLL核心

- VCO范围:750 MHz至825 MHz

- 集成环路滤波器

- 独立、重复的参考输入或分数N PLL有源参考输入的操作

- 输入频率:25 MHz

- 通过引脚捆扎(PPRx)预设频率转换

- 25 MHz、33.33 MHz、50 MHz、66.67 MHz、100 MHz、133.33 MHz、200 MHz或400 MHz

- 最多3份参考时钟输出

- 11对可配置差分输出

- 输出驱动器格式

- 3个输出:HSTL、LVDS、HCSL、1.8 V CMOS、2.5 V/3.3 V CMOS

- 8个输出:HSTL、LVDS或1.8 V CMOS

- 2.5 V或3.3 V单电源操作

应用

- 以太网卡、交换机和路由器

- 基带单元

- SATA和PCI express

- 低抖动、低相位噪声时钟生成

- 异步时钟生成

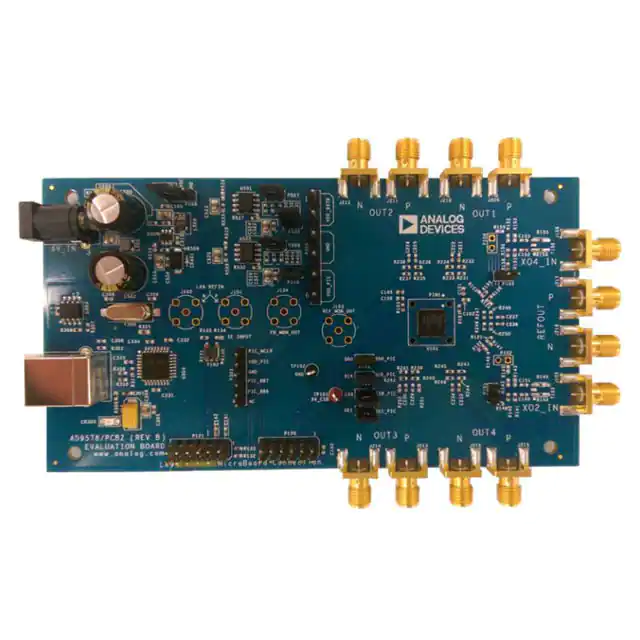

(图片:引出线)