一般说明

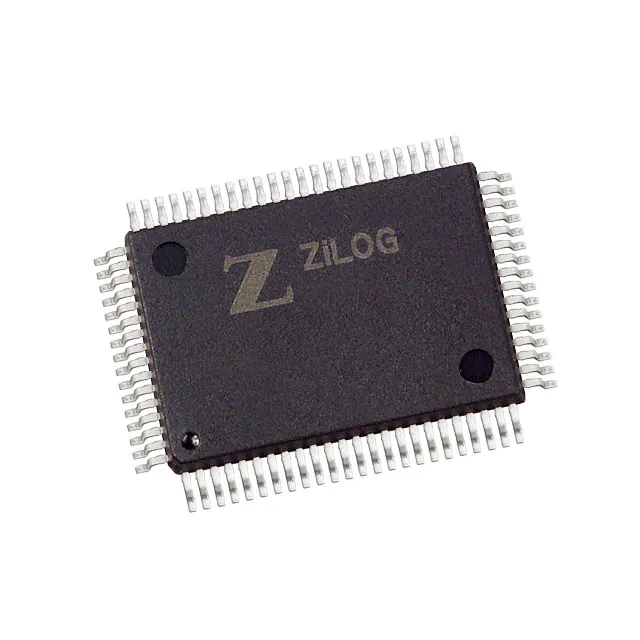

增强型Z80180/Z8S180/Z8L180™ 在与现有Zilog Z80设备完全向后兼容的同时,显著改进了先前的Z80180型号。Z80180/Z8S180/Z8L180现在提供了更快的执行速度、节能模式和EMI噪音降低。这种增强的Z180设计还包括对ASCI、DMA和Icc待机模式功耗的额外功能增强。通过添加“类似ESCC”的波特率发生器(BRG),这两个ASCI现在具有以高达512 Kbps的速率异步传输数据的灵活性和能力。此外,ASCI接收机增加了一个4字节的先进先出(FIFO),可用于缓冲传入数据,以减少超限错误的发生。DMA已被修改,以允许两个DMA通道在设置为从同一外围设备接收DMA请求时“链接”。该特性允许两个DMA通道之间不间断的DMA操作,减少了CPU的干预量(图1)。

Z80180/Z8S180/Z8L180不仅在正常操作过程中消耗的功率比之前的型号少,而且还设计了三种模式,旨在进一步降低功耗。Zilog通过停止外部振荡器和内部时钟,将待机模式期间的Icc功耗降至最低10µa。SLEEP模式通过将CPU置于“停止”状态来降低功耗,从而在片上I/O设备仍在运行时消耗更少的电流。SYSTEM STOP模式将CPU和机上外设置于“停止”模式,从而进一步降低功耗。Z80180/Z8S180/Z8L180设备中实现了一个新的时钟倍频器功能,允许程序员将内部时钟与外部时钟加倍。这通过允许使用较低成本、较低频率的晶体而不是较高成本和较高速度的振荡器来提供系统成本节约。增强型Z180封装在80引脚QFP、68引脚PLCC和64引脚DIP封装中。

特征

■ 代码与Zilog Z80®CPU兼容

■ 扩展指令

■ 两个链式DMA信道

■ 低功耗模式

■ 片上中断控制器

■ 三个片上等待状态发生器

■ 片上振荡器/发生器

■ 扩展的MMU寻址(最多1 MB)

■ 时钟串行I/O端口

■ 两个16位计数器/计时器

■ 两个增强型UART(最高512 Kbps)

■ 时钟速度:6、8、10、20、33 MHz

■ 工作范围:5V(3.3V@20 MHz)

■ 工作温度范围:0°C至+70°C

■ -40°C至+85°C扩展温度范围

■ 三种包装风格

–68针PLCC

–64针DIP

–80针QFP

特色

- 无法使用的

(图片:引出线)