特色

- 高达1GHz Sitara ARM Cortex-A8 32位RISC处理器

- NEON SIMD协处理器

- 32KB的一级指令和32KB的数据缓存,带有单错误检测(奇偶校验)

- 256KB带纠错码(ECC)的二级缓存

- 176KB片上引导ROM

- 64KB的专用RAM

- 仿真和调试-JTAG

- 中断控制器(最多128个中断请求)

- 片上存储器(共享L3 RAM)

- 64KB通用片上存储器控制器(OCMC)RAM

- 所有大师均可访问

- 支持快速唤醒的保留

- 外部存储器接口(EMIF)

- mDDR(LPDDR)、DDR2、DDR3、DDR3L控制器:

- mDDR:2000 MHz时钟(400 MHz数据速率)

- DDR2:266 MHz时钟(532 MHz数据速率)

- DDR3:400 MHz时钟(800 MHz数据速率)

- DDR3L:400 MHz时钟(800 MHz数据速率)

- 16位数据总线

- 1GB的总可寻址空间

- 支持一个x16或两个x8内存设备配置

- 通用内存控制器(GPMC)

- 灵活的8位和16位异步存储器接口,最多可选择七个芯片(NAND、NOR、Muxed NOR、SRAM)

- 使用BCH代码支持4位、8位或16位ECC

- 使用汉明码支持1位ECC

- 错误定位器模块(ELM)

- 与GPMC结合使用,从BCH算法生成的综合症多项式中查找数据错误的地址

- 支持基于BCH算法的每512字节4位、8位和16位块错误定位

- mDDR(LPDDR)、DDR2、DDR3、DDR3L控制器:

- 可编程实时单元子系统和工业通信子系统(PRU-ICSS)

- 支持EtherCAT、PROFIBUS、PROFINET、EtherNet/IP等协议

- 两个可编程实时单元(PRU)

- 32位加载/存储RISC处理器,能够在200 MHz下运行

- 8KB单错误检测(奇偶校验)指令RAM

- 8KB数据RAM,带单错误检测(奇偶校验)

- 带64位累加器的单循环32位乘法器

- 增强型GPIO模块提供移位输入/输出支持和外部信号的并行锁存

- 12KB共享RAM,带单错误检测(奇偶校验)

- 每个PRU可访问的三个120字节寄存器组

- 用于处理系统输入事件的中断控制器(INTC)

- 用于将内部和外部主机连接到PRU-ICSS内部资源的本地互连总线

- PRU-ICSS内部外围设备:

- 一个带流量控制引脚的UART端口,支持高达12 Mbps

- 一个增强型捕获(eCAP)模块

- 两个支持工业以太网的MII以太网端口,如EtherCAT

- 一个MDIO端口

- 电源、复位和时钟管理(PRCM)模块

- 控制待机和深度睡眠模式的进入和退出

- 负责睡眠排序、电源域关闭排序、唤醒排序和电源域打开排序

- 时钟

- 集成15至35 MHz高频振荡器,用于为各种系统和外围时钟生成参考时钟

- 支持子系统和外围设备的单独时钟启用和禁用控制,以降低功耗

- 生成系统时钟的五个ADPLL(MPU子系统、DDR接口、USB和外围设备[MMC和SD、UART、SPI、I2C]、L3、L4、以太网、GFX[SGX530]、LCD像素时钟)

- 权力

- 两个不可切换电源域(实时时钟[RTC]、唤醒逻辑[WAKEUP])

- 三个可切换电源域(MPU子系统[MPU]、SGX530[GFX]、外围设备和基础设施[PER])

- 基于管芯温度、工艺变化和性能(自适应电压缩放[AVS])实现SmartReflex 2B级磁芯电压缩放

- 动态电压频率缩放(DVFS)

- 实时时钟(RTC)

- 实时日期(一周中的日、月、年、日)和时间(小时、分钟、秒)信息

- 内部32.768-kHz振荡器、RTC逻辑和1.1V内部LDO

- 独立上电复位(RTC_PWRONRSTn)输入

- 外部唤醒事件专用输入引脚(EXT_WAKEUP)

- 可编程报警可用于生成PRCM(用于唤醒)或Cortex-A8(用于事件通知)的内部中断

- 可编程报警可与外部输出(PMIC_POWER_EN)一起使用,以启用电源管理IC恢复非RTC电源域

- 外围设备

- 最多两个USB 2.0高速DRD(双角色设备)端口,带有集成PHY

- 最多两个工业千兆以太网MAC(10、100、1000 Mbps)

- 集成交换机

- 每个MAC支持MII、RMII、RGMII和MDIO接口

- 以太网MAC和交换机可以独立于其他功能运行

- IEEE 1588v2精确时间协议(PTP)

- 最多两个控制器局域网(CAN)端口

- 支持CAN版本2 A和B部分

- 最多两个多通道音频串行端口(McASP)

- 发送和接收时钟高达50 MHz

- 每个McASP端口最多四个串行数据引脚,具有独立的TX和RX时钟

- 支持时分复用(TDM)、IC间声音(I2S)和类似格式

- 支持数字音频接口传输(SPDIF、IEC60958-1和AES-3格式)

- 用于发送和接收的FIFO缓冲区(256字节)

- 最多六个UART

- 所有UART支持IrDA和CIR模式

- 所有UART支持RTS和CTS流量控制

- UART1支持完全调制解调器控制

- 最多两个主和从McSPI串行接口

- 最多两个芯片选择

- 最高48 MHz

- 最多三个MMC、SD、SDIO端口

- 1位、4位和8位MMC、SD、SDIO模式

- MMCSD0具有用于1.8V或3.3V操作的专用电源轨

- 高达48 MHz的数据传输速率

- 支持卡检测和写保护

- 符合MMC4.3、SD、SDIO 2.0规范

- 多达三个I2C主接口和从接口

- 标准模式(最高100 kHz)

- 快速模式(最高400 kHz)

- 最多四组通用I/O(GPIO)引脚

- 每组32个GPIO引脚(与其他功能引脚复用)

- GPIO引脚可用作中断输入(每组最多两个中断输入)

- 最多三个外部DMA事件输入,也可用作中断输入

- 八个32位通用定时器

- DMTIMER1是用于操作系统(OS)Tick的1毫秒计时器

- DMTIMER4–DMTIMER7已锁定

- 一个看门狗定时器

- SGX530 3D图形引擎

- 基于平铺的架构每秒提供多达2000万个多边形

- 通用可扩展着色器引擎(USSE)是一个多线程引擎,结合了像素和顶点着色器功能

- 超过Microsoft VS3.0、PS3.0和OGL2.0的高级着色器功能集

- Direct3D Mobile、OGL-ES 1.1和2.0以及OpenMax的行业标准API支持

- 细粒度任务切换、负载平衡和电源管理

- 用于最小CPU交互的高级几何DMA驱动操作

- 可编程高质量图像消除混叠

- 统一内存体系结构中用于操作系统操作的完全虚拟化内存寻址

- LCD控制器

- 最多24位数据输出;每像素8位(RGB)

- 分辨率高达2048×2048(最大126 MHz像素时钟)

- 集成LCD接口显示驱动器(LIDD)控制器

- 集成光栅控制器

- 集成DMA引擎,通过中断或固件定时器从外部帧缓冲区中提取数据,而不会给处理器带来负担

- 512字深度内部FIFO

- 支持的显示类型:

- 字符显示-使用LID控制器对这些显示进行编程

- 无源矩阵LCD显示器-使用LCD光栅显示控制器为无源显示器提供持续图形刷新的定时和数据

- 有源矩阵LCD显示器-使用外部帧缓冲空间和内部DMA引擎将流数据驱动到面板

- 12位逐次逼近寄存器(SAR)ADC

- 每秒200K个样本

- 可以从通过8:1模拟开关多路复用的八个模拟输入中选择任何一个输入

- 可配置为作为4线、5线或8线电阻式触摸屏控制器(TSC)接口操作

- 最多三个32位eCAP模块

- 可配置为三个捕获输入或三个辅助PWM输出

- 最多三个增强型高分辨率PWM模块(eHRPWM)

- 具有时间和频率控制的专用16位时基计数器

- 可配置为六个单端、六个双边缘对称或三个双边缘不对称输出

- 最多三个32位增强型正交编码器脉冲(eQEP)模块

- 设备标识

- 包含电气保险丝场(FuseFarm),其中一些位是工厂可编程的

- 生产ID

- 设备零件号(唯一JTAG ID)

- 设备版本(可由主机ARM读取)

- 包含电气保险丝场(FuseFarm),其中一些位是工厂可编程的

- 调试接口支持

- 用于ARM的JTAG和cJTAG(Cortex-A8和PRCM),PRU-ICSS调试

- 支持设备边界扫描

- 支持IEEE 1500

- 数字移动通信

- 片上增强型DMA控制器(EDMA)有三个第三方传输控制器(TPTC)和一个第三方信道控制器(TPCC),最多支持64个可编程逻辑信道和八个QDMA信道。EDMA用于:

- 与片上存储器之间的传输

- 与外部存储器(EMIF、GPMC、从属外围设备)之间的传输

- 片上增强型DMA控制器(EDMA)有三个第三方传输控制器(TPTC)和一个第三方信道控制器(TPCC),最多支持64个可编程逻辑信道和八个QDMA信道。EDMA用于:

- 处理器间通信(IPC)

- 集成用于IPC和Spinlock的基于硬件的邮箱,用于Cortex-A8、PRCM和PRU-ICSS之间的进程同步

- 生成中断的邮箱寄存器

- 四个启动器(Cortex-A8、PRCM、PRU0、PRU1)

- Spinlock有128个软件分配的锁定寄存器

- 生成中断的邮箱寄存器

- 集成用于IPC和Spinlock的基于硬件的邮箱,用于Cortex-A8、PRCM和PRU-ICSS之间的进程同步

- 安全

- 加密硬件加速器(AES、SHA、RNG)

- 安全引导

- 启动模式

- 通过锁定在PWRONRSTn复位输入引脚上升边缘上的引导配置引脚选择引导模式

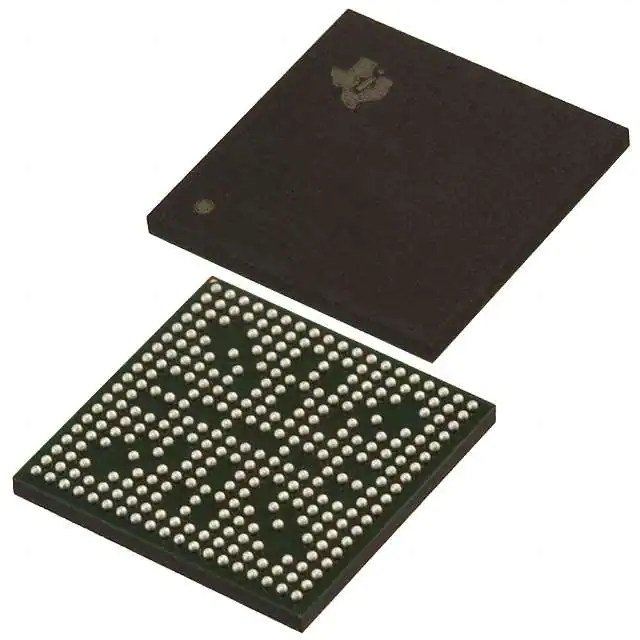

- 包装:

- 298引脚S-PBGA-N298通过通道封装

(ZCE后缀),0.65mm球距 - 324引脚S-PBGA-N324组件

(ZCZ后缀),0.80-mm球距

- 298引脚S-PBGA-N298通过通道封装