一般说明

PAL22V10提供用户可编程逻辑,以减少芯片数量替换传统SSI/MSI门和触发器。

PAL22V10设备实现了熟悉的布尔逻辑传递函数,即乘积之和。PAL设备是驱动固定OR阵列的可编程AND阵列。“与”阵列被编程为创建自定义乘积项,而“或”阵列在输出端对所选项求和。乘积项连接到固定的OR阵列,在输出端具有从8到16的变化分布(参见方框图)。乘积的OR和馈送输出宏单元。每个宏小区可以被编程为注册的或组合的、高活性的或低活性的。输出配置由控制每个宏小区中的两个多路复用器的两个熔断器确定。

AMD的FusionPLD程序允许使用各种流行的标准设计工具实现PAL22V10设计。通过与FusionPLD合作伙伴的密切合作,AMD证明这些工具提供了准确、高质量的支持。通过确保第三方工具可用,可以降低成本,因为设计师不必为每个设备购买整套新工具。FusionPLD程序还大大缩短了设计时间,因为设计师可以使用已经安装并熟悉的工具。

与众不同的特点

·快至7.5-ns传播延迟和91MHz fwAx(外部)

·10个宏单元,可编程为注册或组合,高活性或低活性,以满足应用需求

·不同的产品术语分布允许复杂功能的每个输出最多16个产品术语

·用于初始化的全局异步重置和同步预设

·通电复位用于初始化,寄存器预加载用于可测试性广泛的第三方软件和·通过FusionPLD合作伙伴提供程序员支持

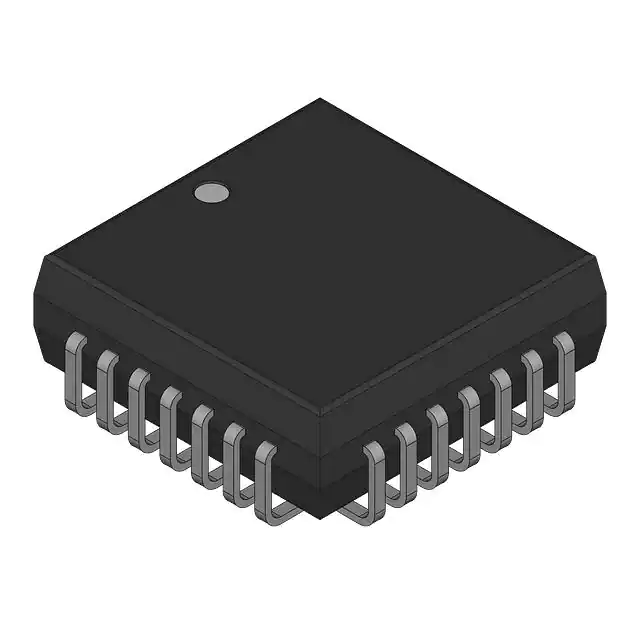

·24针SKINNYIP、24针扁平封装和28针PLCC和LCC封装节省空间

(图片:引出线)