Altera ClassicTM EP610SC-20设备为高速、低功耗逻辑集成提供了解决方案。基于先进的CMOS技术制造的EP610SC-20器件还具有Turbo专用版本,这在本数据表中有所描述。

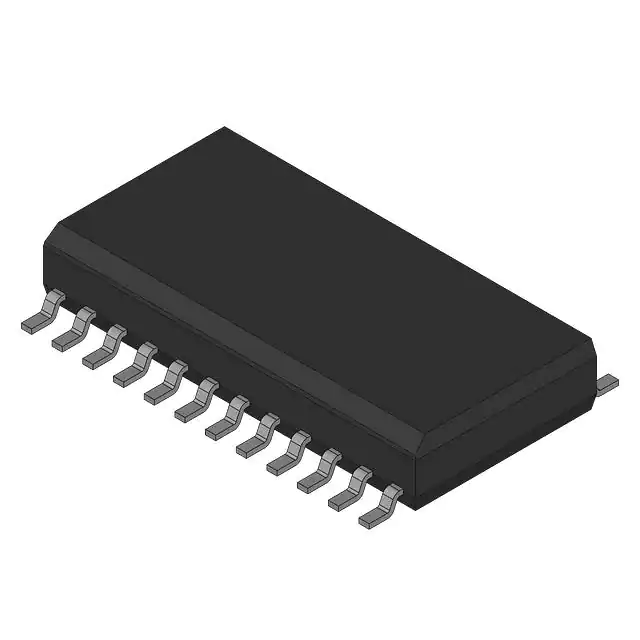

经典设备支持100%TTL模拟,可以轻松集成多个PAL和GAL类型的设备,其可用门的密度从300到900。经典系列提供低至10ns的引脚到引脚逻辑延迟和高达100MHz的计数器频率。经典器件有多种封装形式,包括陶瓷双列直插式封装(CerDIP)、塑料双列直插封装(PDIP)、塑料J形引线芯片载体(PLCC)、陶瓷J形引线晶片载体(JLCC)、引脚栅格阵列(PGA)和小外形集成电路(SOIC)封装。

EP610SC-20设备具有16个宏单元、4个专用输入引脚、16个I/O引脚和2个全局时钟引脚每个宏小区可以访问来自全局总线的信号,该全局总线由以下真形式和补码形式组成:

专用输入以及宏单元输出或I/O输入的真形式和补码形式。这个第1类信号是宏单元9至16中寄存器的专用全局时钟输入。这个第2类信号是宏单元1至8中寄存器的专用全局时钟输入。

基于EPROM的经典器件可以在不牺牲性能的情况下降低有功功耗。这种降低的功耗使Classic系列非常适合各种低功耗应用。

经典设备是在窗口封装中经过100%通用测试的设备,可以用紫外线(UV)擦除,从而快速实现设计更改。经典设备使用积和逻辑和可编程寄存器。积和逻辑提供了一种可编程的AND/固定OR结构,可以实现多达八个积项的逻辑。可编程寄存器可单独编程用于D、T、SR或JK触发器操作,或可被旁路用于组合操作。此外,宏单元寄存器可以通过全局时钟或到AND阵列的任何输入或反馈路径单独计时。Altera专有的可编程I/O体系结构允许设计人员对输出和反馈路径进行编程,以便在活动高模式和活动低模式下进行组合或注册操作。这些特性使得可以同时实现各种逻辑功能。

Altera的MAX+PLUS II开发系统支持经典设备,这是一个单一的集成包,提供原理图、文本(包括VHDL、Verilog HDL和Altera硬件描述语言(AHDL))和波形设计输入、编译和逻辑合成、仿真和时序分析以及设备编程。MAX+PLUS II软件提供EDIF 2 0 0和3 0 0、LPM、VHDL、Verilog HDL和其他接口,用于其他基于工业标准PC和工作站的EDA工具的额外设计输入和仿真支持。MAX+PLUS II软件在基于Windows的PC、Sun SPARCstation、HP 9000 Series 700/800和IBM RISC System/6000工作站上运行。这些设备还包含板载逻辑测试电路,以允许在标准生产流程期间验证功能和交流规格。

特色

| ■高性能,16宏蜂窝经典EPLD –组合速度吨局部放电快至10纳秒 |

–高达125 MHz的流水线数据速率

■可编程I/O架构,具有多达20个输入或16个输出和2个时钟引脚

■EP610和EP610I设备与引脚、功能和编程文件兼容

■可编程时钟选项,用于所有寄存器的独立计时

■宏单元可单独编程为D、T、JK或SR触发器,或用于组合操作

■以下软件包中提供(请参见图7):

–24针小外形集成电路(仅限塑料SOIC)

–24针陶瓷和塑料双列直插式封装(CerDIP和PDIP)

–28针塑料J形引线芯片载体(PLCC)

(图片:引出线)