本节提供设备功能的高级概述。下图显示了设备中的主要功能单元。

尽管本文件是从MPC8544E的角度编写的,但大多数材料适用于其他家族成员,如MPC8547E、MPC8545E和MPC8543E。当出现特定的差异时,例如引脚输出差异和处理器频率范围时,它们被识别为这样。

有关特定PVR和SVR编号,请参阅MPC8548E PowerQUICC III集成主机处理器参考手册。

特色

- 嵌入式e500核心,可扩展至1.5 GHz

- 双调度超级定标器,7级流水线设计,无乱序问题和执行

- 1333 MHz下的3065 MIPS(估计Dhrystone 2.1)

- 集成L1/L2缓存

- 一级缓存-32 KB数据和32 KB指令缓存,支持行锁定

- 二级缓存-512 KB(8路集合关联);512 KB/256 KB/128 KB/64 KB可用作SRAM

- L1和L2硬件一致性

- L2可配置为SRAM、缓存或存储缓存

- 集成DDR内存控制器,完全支持ECC,支持:

- 200 MHz时钟速率(400 MHz数据速率),64位,2.5V/2.6V I/O,DDR SDRAM

- 266 MHz时钟速率(高达533 MHz数据速率)DDR2 SDRAM

- 双精度嵌入式标量和矢量浮点APU

- 内存管理单元(MMU)

- 支持DES、3DES、MD-5、SHA-1/2、AES、RSA、RNG、Kasumi F8/F9和ARC-4加密算法的集成安全引擎

- 多PCI接口支持

- 64位PCI 2.2总线控制器(最高66 MHz,3.3V I/O)

- 64位PCI-X总线控制器(最高133 MHz,3.3V I/O),或

- 灵活配置两个32位PCI控制器

- 四个片上三倍速以太网控制器(GMAC),支持10和100 Mbps,以及具有MII、RMII、GMII、RGMII、RTBI和TBI物理接口的1-Gbps以太网/802.3网络。

- TCP/IP校验和加速

- 高级QoS功能

- 通用I/O

- 串行RapidIO和PCI Express高速互连接口,支持

- 单x8 PCI Express,或

- 单x4 PCI Express和单4x串行RapidIO

- 片上网络(OCeaN)交换结构

- 集成四通道DMA控制器

- 双I²C接口和双通用异步接收机/发射机(DUART)支持

- 可编程中断控制器(PIC)

- 通用并行I/O(GPIO)

- IEEE®1149.1 JTAG测试访问端口

- 1.1V核心电压,3.3V和2.5V I/O

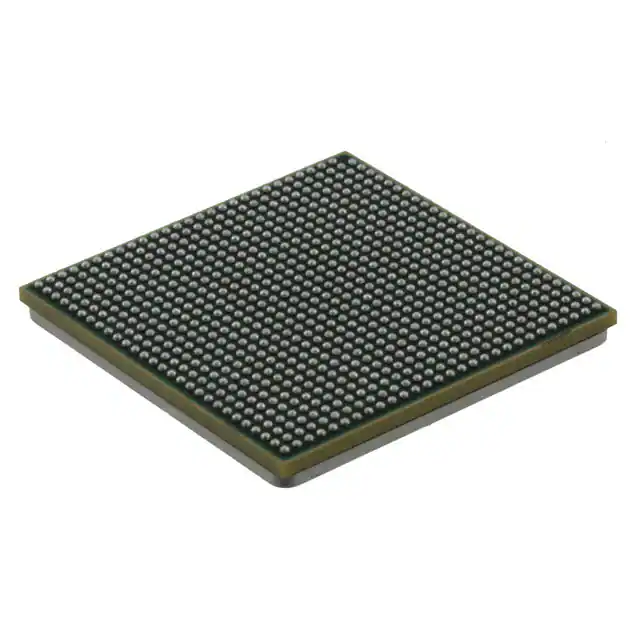

- 783针FC-BGA封装

- 该产品包含在NXP®的产品寿命计划中,在推出后至少可保证10年的供应