特征

·每个数据传输周期指定的转换

·单差分对消除了多差分对-

通道倾斜

·易于PCB布局的流通引脚

·400 Mbps串行总线LVDS带宽(40

MHz时钟)

·1字节数据加2的10位并行接口

控制位

·时钟上的可编程边沿触发器

·额定27Q负载的总线LVDS串行输出

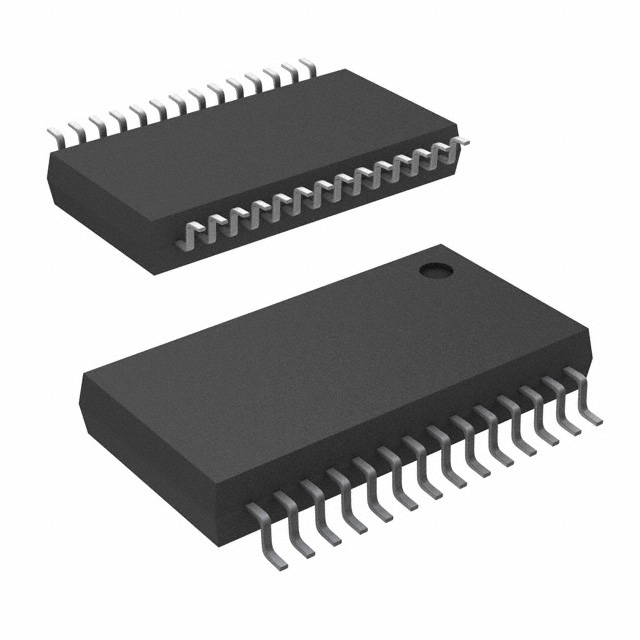

·小型28导联SSOP包DB

说明

DS92LV1021A将一条10位宽的并行LVCMOS/LVTTL数据总线转换为一条带嵌入式时钟的高速总线LVDS串行数据流。

DS92LV1021A可以通过背板或电缆传输数据。单差分对数据路径使PCB设计更容易。此外,减少的电缆、PCB迹线数量和连接器尺寸大大降低了成本。由于一个输出同时串行传输时钟和数据位,因此消除了时钟到-

数据和数据对数据的偏斜。断电引脚在设备未使用时通过减少电源电流来节省电力。在Serializer通电后,您可以选择激活同步模式或在同步到随机数据功能中使用TI的反序列化器之一。通过使用同步模式,解串器将在指定的锁定时间内建立对信号的锁定。此外,嵌入式时钟每12位周期指定总线上的转换。这消除了由于充电电缆条件导致的传输错误。

此外,您可以将DS92LV1021A输出引脚置于三态,以实现高阻抗状态。PLL可以锁定在16

MHz和40MHz。

(图片:引线/示意图)