快速、高精度的差分输入级允许在共模范围内从-2.0 V到+3.0 V的各种信号的一致传播延迟。输出是与ECL 10 K和10 KH逻辑系列完全兼容的互补数字信号。输出提供足够的驱动电流,以直接驱动终止于50至2 V的传输线。包括锁存器输入,允许跟踪、跟踪保持或采样保持操作模式。

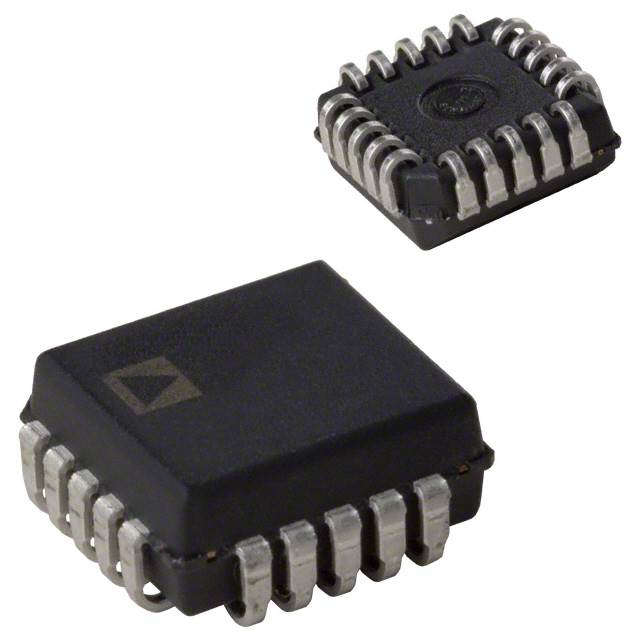

ADCMP565BP采用20导联PLCC封装。

特色

- 输入到输出的300 ps传播延迟

- 50ps传播延迟色散

- 差分ECL兼容输出

- 差速器锁闩控制

- 鲁棒输入保护

- 输入共模范围:-2.0 V至+3.0 V

- 输入差动范围±5 V

- 电源灵敏度抑制大于65 dB

- 200 ps最小脉宽

- 5GHz等效输入上升时间带宽

- 160 ps的典型输出上升/下降

- SPT 9689替换