The NL17VHC1GT50DF1G is a single gate noninverting buffer fabricated with silicon gate CMOS technology. It achieves high speed operation while maintaining CMOS low power dissipation. The internal circuit is composed of three stages, including a buffer output which provides high noise immunity and stable output. The device input is compatible with low threshold input thresholds and the output has a full CMOS level output swing. The input protection circuitry on this device allows overvoltage tolerance on the input,allowing the device to be used as a logic-level translator from 1.65 V logic to 5.5V CMOS The NL17VHC1GT50DF1G input structure provides protection for input voltages up to 5.5V , regardless of the supply voltage. The output structures also provide protection when VCC = 0V. These input and output structures help prevent device destruction caused by supply voltage - input/output voltage mismatch, battery backup, hot insertion, etc.

Feature

- High Speed: tPD = 3.5ns (Typ) at VCC = 5V

- Low Power Dissipation: ICC = 1µA (Max) at TA = 25°C

- Low threshold Inputs, TTL compatible if Vcc= 5 V: VIL = 0.8V; VIH = 2.0V

- CMOS-Compatible Outputs: VOH > 0.8VCC ; VOL < 0.1VCC @Load

- Power Down Protection Provided on Inputs and Outputs

- Balanced Propagation Delays

- Pin and Function Compatible with Other Standard Logic Families

- Chip Complexity: FETs = ≤ 100

- Pb-Free Packages are Available

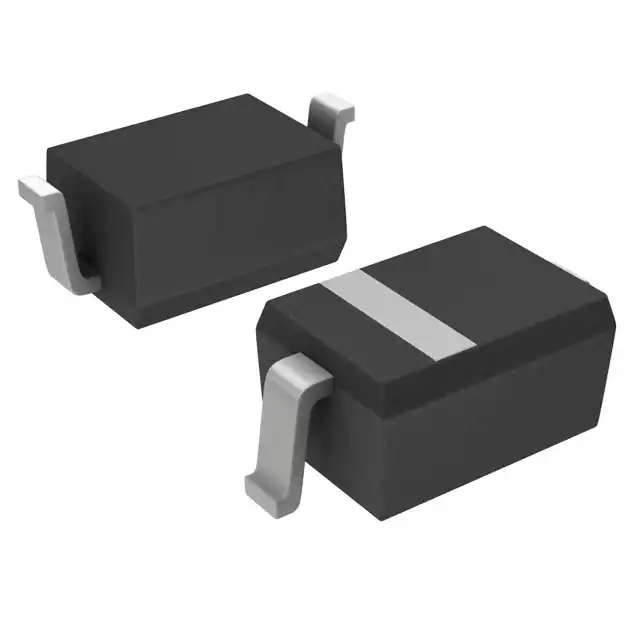

(Picture: Pinout)