Feature

- tPD 2.6ns (typical) at VCC = 5V Extremely High Speed

- Designed for 1.65 to 5.5V VCC Operation

- 5V Tolerant Inputs, Interface Capability with 5V TTL Logic

- LVTTL Compatible

- LVCMOS Compatible

- 24mA Balanced Output Sink and Source Capability

- Near zero static supply current in all three logic states (10µA) reduces system power requirements

- Replacement for NC7SZ74

- 2000V Human Body Model, 200V Machine Model High ESD Ratings

- FET = 64 Chip Complexity

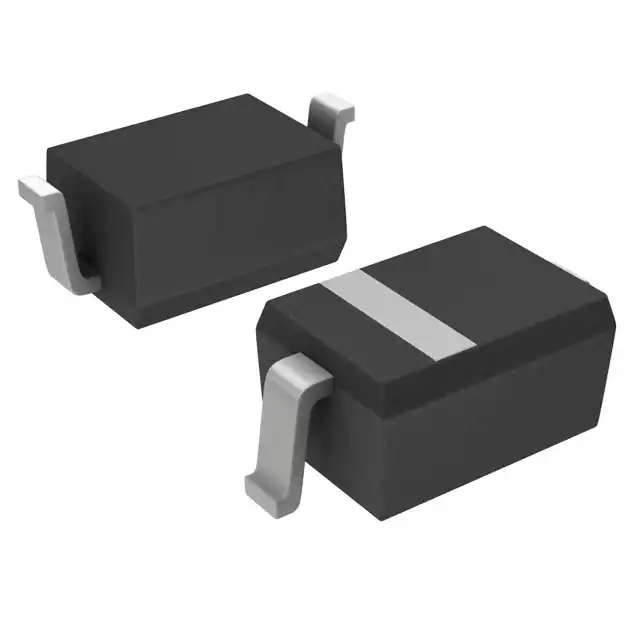

(Picture: Pinout)