DESCRIPTION

The SY55852UKG is a flip-flop used to synchronize data to a clock. Its differential output will reproduce and remember the value on its input at the rising edge of the clock. In addition, an asynchronous, level sensitive reset is provided. For a synchonous reset, the SY55851U AnyGate TM can be used.

SY55852UKG inputs can be terminated with a single resistor between the true and complement pins of a given input.

The SY55852UKG is a member of Micrel's SuperLite TM family of high-speed CML logic. This family features very small packaging and 2.3V to 5.7V operation.

FEATURES

■2.5GHz min. fMAx

■2.3V to 5.7V power supply

■Single bit register memory

■Synchronizes 1 bit of data to a clock

■Optimized to work with SuperLite rnm family

■Fully differential

■Accepts CML, PECL, LVPECL input logic levels

■Source terminated CML outputs for fast edge rates

■Available in a tiny 10-pin MSOP

APPLICATIONS

■High-speed logic

■OC-48 communication systems

Feature

- 2.5GHz min. fMAX

- 2.3V to 5.7V power supply

- Single bit register memory

- Synchronizes 1 bit of data to a clock

- Optimized to work with SuperLite™ family

- Fully differential

- Accepts CML, PECL, LVPECL input logic levels

- Source terminated CML outputs for fast edge rates

- Available in a tiny 10-pin MSOP

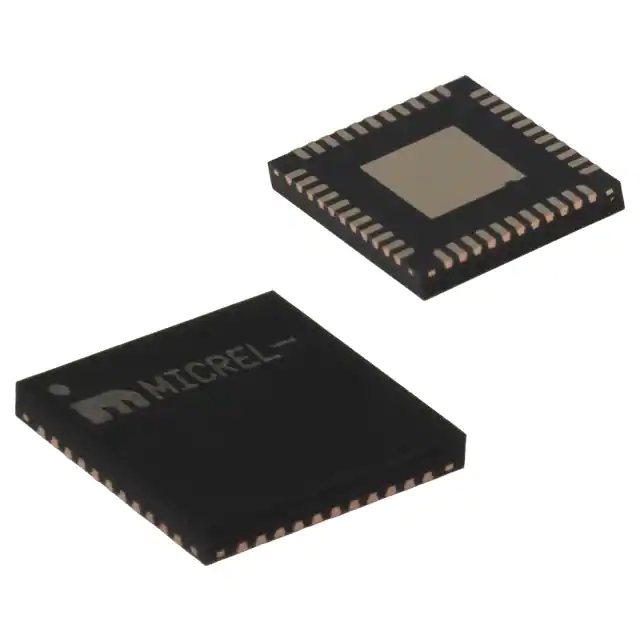

(Picture: Pinout)