This single 2-input positive-OR gate performs the Boolean function in positive logic.

Feature

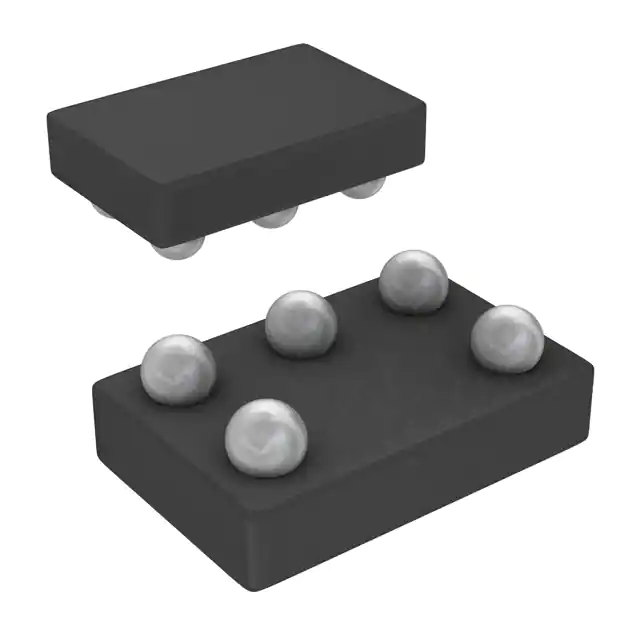

- Available in the ultra-small 0.64 mm2 package (DPW) with 0.5-mm pitch

- Low static-power consumption

(ICC = 0.9 μA Max) - Low dynamic-power consumption

(Cpd = 4.3 pF Typ at 3.3 V) - Low input capacitance (CI = 1.5 pF Typ)

- Low noise – overshoot and undershoot

<10% of VCC - Ioff Supports live insertion, partial-power-down

mode, and back drive protection - Input hysteresis allows slow input transition and better switching noise immunity at the

input (Vhys = 250 mV typ at 3.3 V) - Wide operating VCC range of 0.8 V to 3.6 V

- Optimized for 3.3-V operation

- 3.6-V I/O Tolerant to support mixed-mode signal operation

- tpd = 4.6 ns Max at 3.3 V

- Suitable for point-to-point applications

- Latch-up performance exceeds 100 mA

Per JESD 78, Class II - ESD performance tested Per JESD 22

- 2000-V Human-body model

(A114-B, Class II) - 1000-V Charged-device model (C101)

- 2000-V Human-body model