Each input channel on the AD8156ABCZ has a programmable input equalizer to compensate for signal loss over a backplane.

The AD8156ABCZ high speed inputs are compatible with both ac-coupled and dc-coupled 3.3 V, 2.5 V, or 1.8 V CML, as well as 3.3 V LVPECL data levels. The control interface is LVTTL- and LVCMOS-compatible at 3.3 V. All input and output termination resistors are integrated for ease of layout and to minimize impedance mismatch. Input equalization and unused outputs can be individually disabled to minimize power dissipation.

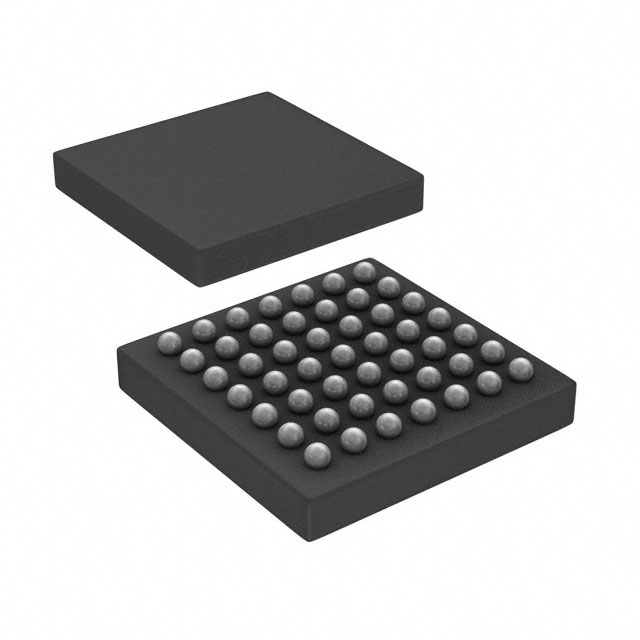

The AD8156ABCZ is packaged in a 49-ball, 8 mm × 8 mm, BGA package with a 1 mm ball pitch. It operates over the industrial temperature range of −40°C to 85°C.

Feature

- 4 × 4, fully differential, nonblocking array

- Configurable for dual 2 × 2 operation

- DC to 6.25 Gbps per channel, NRZ data rate

- Programmable input equalization compensates for over 40” of FR-4 at 6.25 Gbps

- Multicast and broadcast modes of operation

- Programmable output swing100 mV p-p to 1.6 V p-p differential

- Power supply: 3.3 V (±10%)

- Low power No EQ: 400 mW typical Maximum EQ: 700 mW typical

- Inputs: ac-coupled or dc-coupled

- Wide set of dc-coupled input standards 3.3 V/2.5 V/1.8 V CML or 3.3 V LVPECL

- Control: LVTTL- or LVCMOS-compatible

- Low additive jitter: 25 ps p-p typical

Applications

- SONET/SDH

- Gigabit Ethernet

- XAUI

- Fibre Channel

(Picture: Pinout)