Intel Serial or quad-serial FPGA configuration in devices that support active serial (AS) x1 or AS x41 configuration schemes. Reprogrammable memory more than 100,000 program-erase cycles. Write protection support for memory sectors using status register bits. Fast read, extended dual input fast read, and extended quad input fast read of the entire memory using a single operation code. Reprogrammable with an external microprocessor using the SRunner software driver. In-system programming (ISP) support with the SRunner software driver. ISP support with Intel® FPGA Download Cable II, Intel® FPGA Download Cable, or Intel® FPGA Ethernet Cable. By default, the memory array is erased and the bits are set to 1.

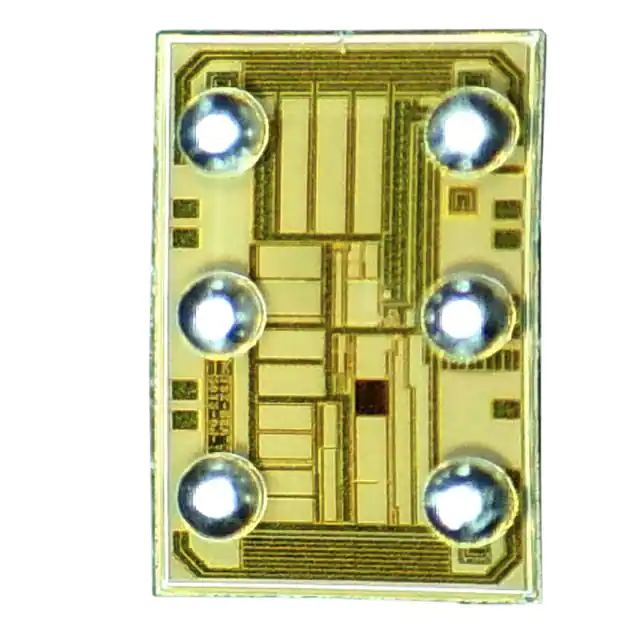

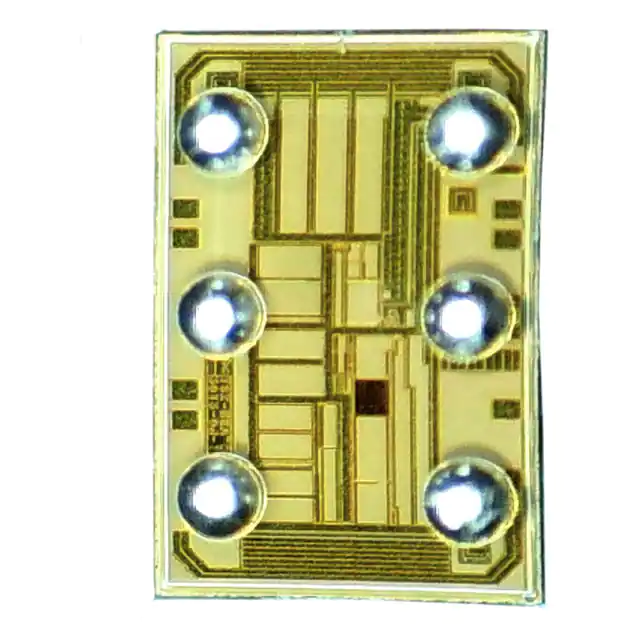

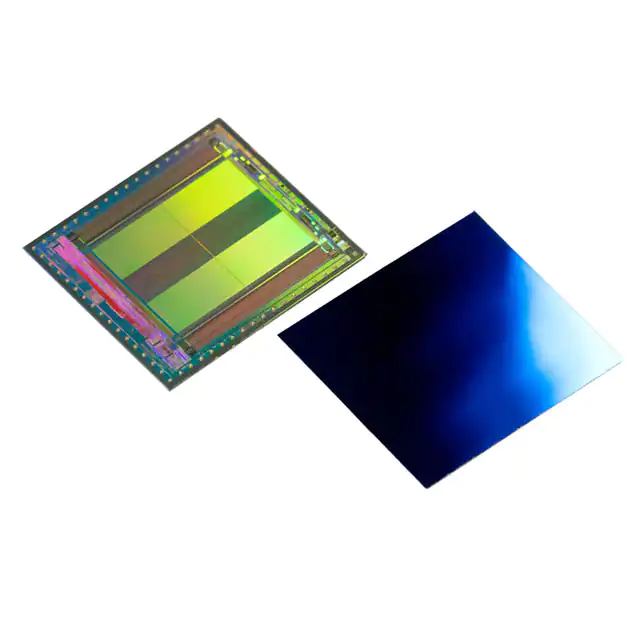

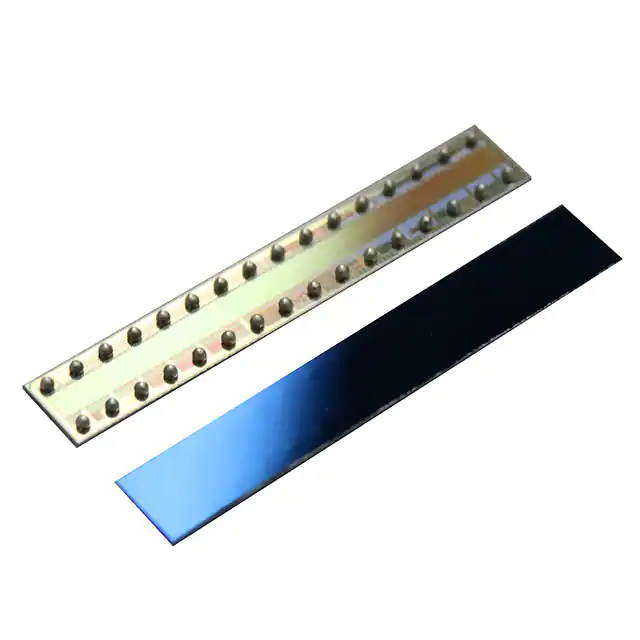

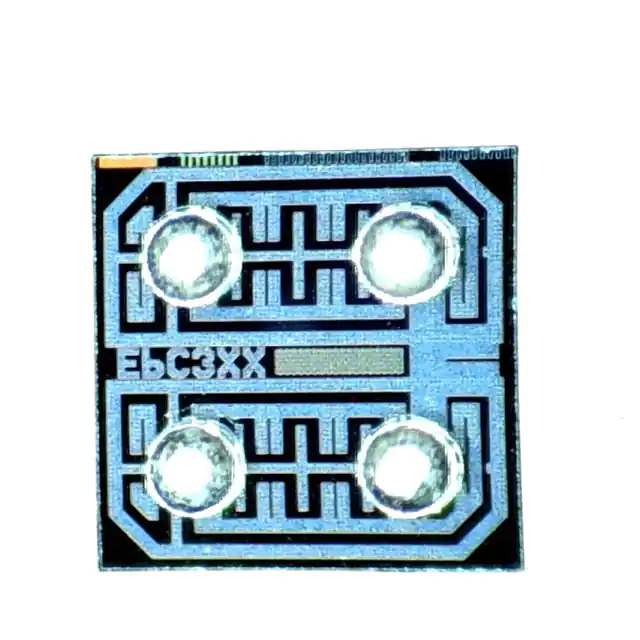

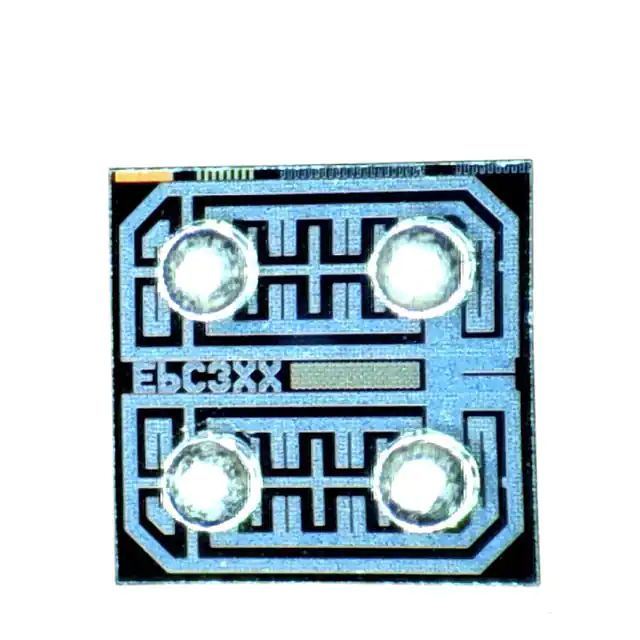

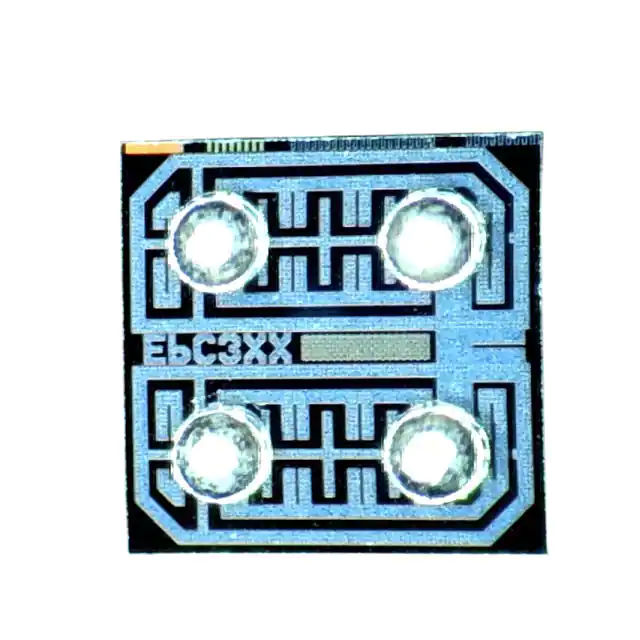

The EPCQ4A, EPCQ16A, and EPCQ32A devices are available in 8-pin SOIC packages. The EPCQ64A and EPCQ128ASI16N devices are available in 16-pin SOIC packages.

EPCQ-A devices support active and standby power modes. When the nCS signal is low, the device is enabled and is in active power mode. The FPGA is configured while the EPCQ-A device is in active power mode. When the nCS signal is high, the device is disabled but remains in active power mode until all internal cycles are completed, such as write or erase operations. The EPCQ-A device then goes into standby power mode. The ICC1 and ICC0 parameters list the VCC supply current when the device is in active and standby power modes.

Feature

EPCQ-A devices offer the following features:

• Serial or quad-serial FPGA configuration in devices that support active serial (AS) x1 or AS x4(1) configuration schemes

• Low cost, low pin count, and non-volatile memory

• 2.7-V to 3.6-V operation

• Available in 8-pin small-outline integrated circuit (SOIC) package for EPCQ4A, EPCQ16A, and EPCQ32A devices

• Available in 16-pin SOIC package for EPCQ64A and EPCQ128A devices

• Reprogrammable memory more than 100,000 program-erase cycles

• Write protection support for memory sectors using status register bits

• Fast read, extended dual input fast read, and extended quad input fast read of the entire memory using a single operation code

• Reprogrammable with an external microprocessor using the SRunner software driver

• In-system programming (ISP) support with the SRunner software driver

• ISP support with Intel® FPGA Download Cable II, Intel FPGA Download Cable, or Intel FPGA Ethernet Cable

• By default, the memory array is erased and the bits are set to 1

• More than 20-year data retention

• Supports JEDEC standard Serial Flash Discoverable Parameter (SFDP)