FPGA Master Serial Mode Summary

The I/O and logic functions of the Configurable Logic Block (CLB) and their associated interconnections are established by a configuration program. The program is loaded either automatically upon power up, or on command, depending on the state of the three FPGA mode pins. In Master Serial mode, the FPGA automatically loads the configuration program from an external memory. The Xilinx PROMs have been designed for compatibility with the Master Serial mode.

Upon power-up or reconfiguration, an FPGA enters the Master Serial mode whenever all three of the FPGA modeselect pins are Low (M0=0, M1=0, M2=0). Data is read from the PROM sequentially on a single data line. Synchronization is provided by the rising edge of the temporary signal CCLK, which is generated during configuration.

Master Serial Mode provides a simple configuration interface. Only a serial data line and two control lines are required to configure an FPGA. Data from the PROM is read sequentially, accessed via the internal address and bit counters which are incremented on every valid rising edge of CCLK.

If the user-programmable, dual-function DIN pin on the FPGA is used only for configuration, it must still be held at a defined level during normal operation. The Xilinx FPGA families take care of this automatically with an on-chip default pull-up resistor.

Feature

- One-time programmable (OTP) read-only memory designed to store configuration bitstreams of Xilinx® FPGAs

- Simple interface to the FPGA; requires only one user I/O pin

- Cascadable for storing longer or multiple bitstreams

- Programmable reset polarity (active High or active Low) for compatibility with different FPGA solutions

- XC17128E/EL, XC17256E/EL, XC1701, and XC1700L series support fast configuration

- Low-power CMOS floating-gate process

- XC1700E series are available in 5V and 3.3V versions

- XC1700L series are available in 3.3V only

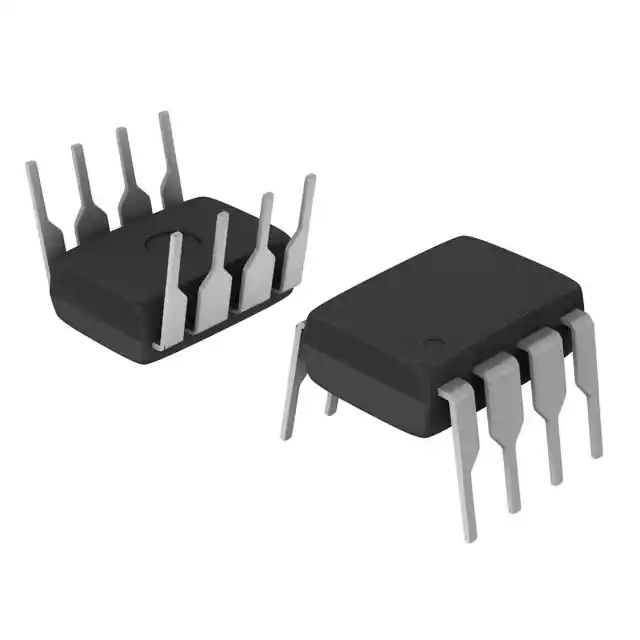

- Available in compact plastic packages: 8-pin SOIC, 8- pin VOIC, 8-pin PDIP, 20-pin SOIC, 20-pin PLCC, 44- pin PLCC or 44-pin VQFP

- Programming support by leading programmer manufacturers

- Design support using the Xilinx Alliance and Foundation™ software packages

- Guaranteed 20 year life data retention

- Lead-free (Pb-free) packaging available