The ADP7105ACPZ-3.3-R7 is a CMOS, low dropout (LDO) linear regulator that operates from 3.3 V to 20 V and provides up to 500 mA of output current. This high input voltage LDO is ideal for regulation of high performance analog and mixed-signal circuits operating from 1.22 V to 19 V rails. Using an advanced proprietary architecture, the ADP7105ACPZ-3.3-R7 provides high power supply rejection and low noise, and achieves excellent line and load transient response with only a small 1 μF ceramic output capacitor.

APPLICATIONS Regulation of noise sensitive applications: ADC and DAC circuits, precision amplifiers, high frequency oscillators, clocks, and PLLs Communications and infrastructure Medical and healthcare Industrial and instrumentation

Feature

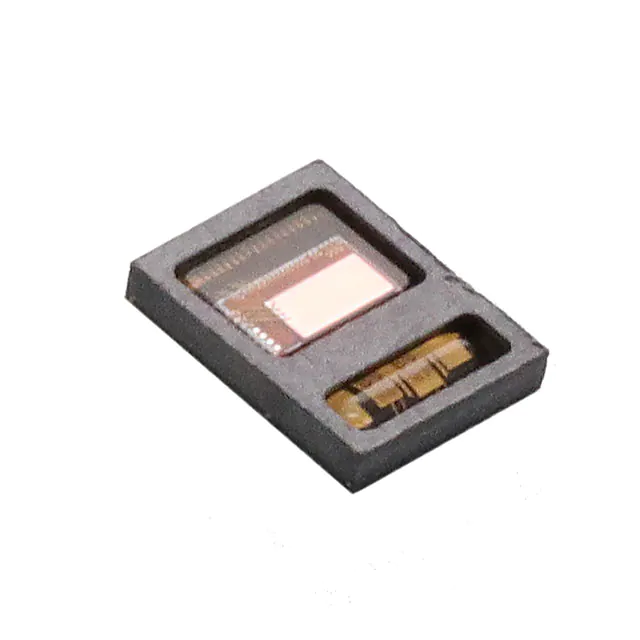

Input voltage range: 3.3 V to 20 V Maximum output current: 500 mA Low noise: 15 μV rms for fixed output versions PSRR performance of 60 dB at 10 kHz, VOUT = 3.3 V Reverse current protection Low dropout voltage: 350 mV at 500 mA Initial accuracy: ±0.8% Accuracy over line, load, and temperature 2% to +1%, TJ = 40℃ to +125℃ 1.25% to +1%, TJ = 0℃ to +85℃ Low quiescent current: 900 μA at VIN = 10 V, IOUT = 500 mA Low shutdown current: <50 μA at VIN = 12 V, stable with small 1 μF ceramic output capacitor 3 fixed output voltage options: 1.8, 3.3 V and 5 V Adjustable output from 1.22 V to 19 V Programmable soft start for inrush current control Foldback current-limit and thermal overload protection User programmable precision UVLO/enable Power-good indicator 8-lead LFCSP and 8-lead SOIC packages