Marvell打造首个3nm SerDes和并行互连

着眼于当今的重型数据基础设施,Marvell在台积电的3nm工艺上实施了SerDes和并行互连技术。2023年4月26日作者:杰克·赫兹

虽然半导体行业传统上专注于晶体管,但互连现在也受到了关注。有许多因素促成了这种兴趣,包括时钟频率的增加、节点尺寸的减小以及小芯片等新技术。

上周,漫威科技宣布首次在3nm节点上成功展示了其先进的半导体互连技术。在这篇文章中,我们将关注互连的重要性日益增长,以及Marvell在台积电3nm工艺上最新宣布的SerDes和并行互连技术。

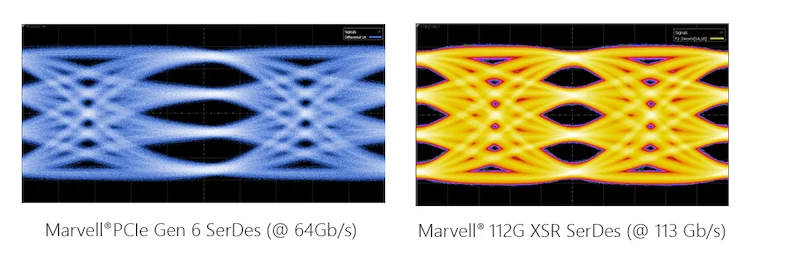

Marvell的3nm SerDes眼图。图片由Marvell Technology提供

现代芯片的互连

在当今的半导体行业中,互连已经成为芯片设计的一个主要瓶颈。

一个主要原因是现代芯片中互连寄生现象日益突出。晶体管节点尺寸的减小导致器件到器件互连具有更小的几何形状和更大的电阻。同样,芯片的集成度越来越高,这意味着电感和电容耦合产生的寄生效应正成为设计师们更加关注的问题。其他因素,如时钟频率的增加也起到了作用。

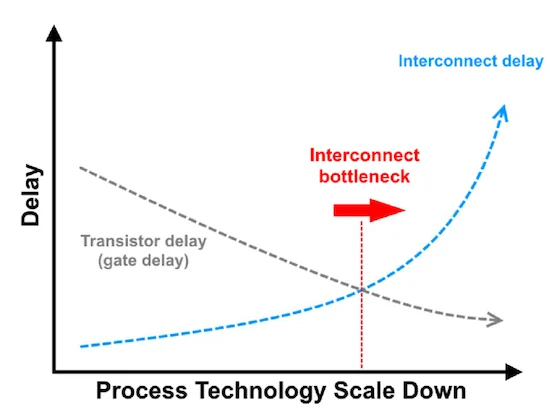

随着工艺技术的规模缩小,互连延迟远远超过晶体管栅极延迟。图片由Bohr等人提供。

互连寄生效应增加的结果是,互连延迟已成为比晶体管延迟更大的瓶颈,这意味着互连是芯片速度的最大瓶颈。以同样的方式,互连寄生效应已经成为整个芯片功耗的主要贡献者。

下一波计算中小芯片的激增进一步加剧了这一问题的严重性,因为下一波计算是由多个通过高速互连连接的小芯片组成的。为了让半导体行业继续发展并提供更高的性能,开发人员必须创新当前的互连设计。

Marvell缩小SerDes和并行互连

Marvell最近发布了一系列用于高级半导体互连的SerDes和并行互连解决方案。早在2020年,Marvell就发布了业界首款用于数据中心的112 G 5nm SerDes,这是该公司为未来计算基础设施开发高性能芯片间互连的努力的一部分。

上周,该公司继续进行这些研发工作,宣布在3nm节点上展示其互连技术。具体而言,该公司声称,它在台积电的3nm节点上实现了122 G XSR SerDes、Long Reach SerDes,PICe Gen 6 SerDes和240 Tbps并行管芯到管芯互连。

Marvell表示,向3nm节点的转变将有助于该公司为小芯片、定制ASIC、以太网物理层设备等应用解锁更低功耗和更高性能的互连。