针对汽车,Infineon Spins业界首款LPDDR闪存

为了满足汽车区域架构的新需求,Infineon将闪存与LPDDR接口相结合,以实现比xSPI NOR闪存更高的性能和可扩展性。2023年4月20日Jeff Child

随着汽车转向软件定义的汽车架构,下一代设计面临着内存问题。由于多种原因,传统的xSPI NOR闪存无法满足这些需求。为了满足这些需求,英飞凌科技公司今天宣布了业界首款LPDDR闪存。

这种新的闪存设备被称为SEMPER X1,它借鉴了已有10年历史的LPDRR4 DRAM的LPDDR接口方案,并将其应用于闪存。

SEMPER XI从DRAM世界借用了LPDDR接口方案,以满足汽车中新兴的计算需求。

在这篇文章中,我们讨论了LPDDR闪存开发旨在解决的问题,我们考察了新技术的好处,并分享了我们采访英飞凌营销和应用副总裁Sandeep Krishnegowda时的观点。

汽车的性能和密度存储器需求

Krishnegowda表示,在下一代汽车中,既需要更多的闪存,也需要更快的性能闪存。汽车向分区架构的转变要求实时处理,这需要比当今标准NOR闪存更高的性能。

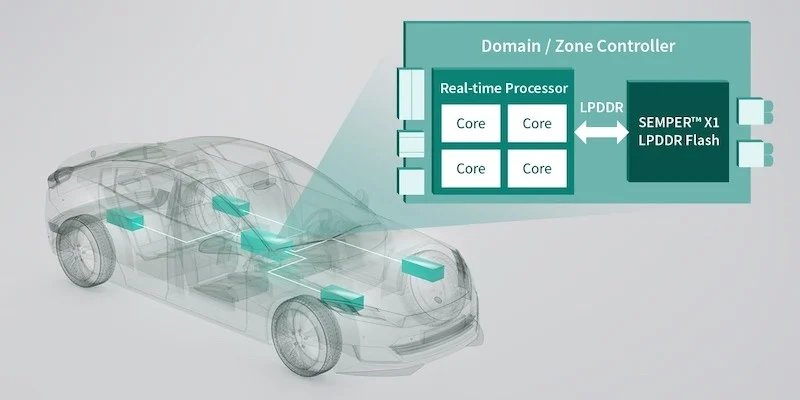

域和区域控制器整合了许多安全关键功能,并且必须实时处理大量数据。(点击图片放大)

如上图所示,这些新车设计在整个车辆上都有区域控制器(绿色)。Krishnegowda说:“这些区域控制器有很多实时计算需求。”。“他们不仅仅将这些数据传递给中央ECU。这些区域控制器需要处理安全关键功能,如制动、转向和动力总成。”

为了能够处理这些实时处理需求,汽车区域控制器不得不不断提高性能水平。Krishnegowda说:“4K DMIPS很常见,现在区域控制器将使用10K、12K和16K DMIPS。”。这种更复杂的计算超出了内置内置闪存的控制器所能处理的范围。

需要更快的外部闪存访问

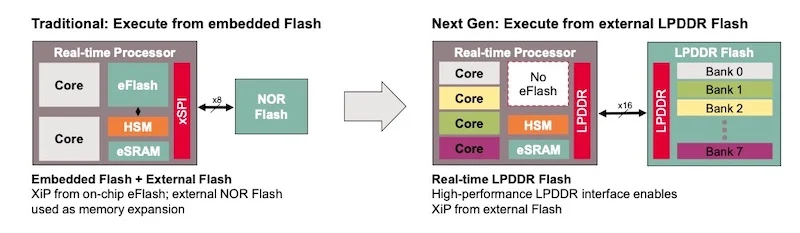

下一代汽车设计中的计算需求推动了人们远离CPU核心和板载闪存的实时处理器。这些处理器正在被没有嵌入式闪存的高性能多核处理器所取代。

事实上,在这些处理器使用的先进半导体工艺节点上,由于处理器和存储器在半导体技术进步方面的不匹配,添加板载闪存并不具有成本效益。

下一代汽车设计的需求要求转向从外部闪存执行的快速实时多核处理器。

在先进的工艺节点上,符合汽车标准的嵌入式闪存技术面临着高成本(芯片面积)和缺乏可扩展性的挑战。所有这些都与需要更多闪存来支持汽车中不断增长的代码大小和复杂性的事实相结合。而且,在接口方面,标准的xSPI NOR闪存无法满足实时就地执行(XiP)性能要求。

正是考虑到了这一点,英飞凌创建了这种新的内存类别,称为LPDDR闪存。Krishnegowda表示:“我们与一些一级原始设备制造商合作,定义了这一类LPDDR闪存,以解决对多核CPU执行实时计算需求日益增长的问题。”。“在LPDDR闪存中,您有多个内存组,因此,当您有多核心时,任何核心都可以与任何一个内存组通信,因为这本质上是随机访问。”

Krishnegowda说,这明显提高了执行速度。他说:“如果你将其与标准的Octal(x8)xSPI NOR闪存设备进行比较,那么改用LPDDR闪存会使你的性能提高20倍。”。“这就是您所需要的,以便将过去在处理器内计算的内容移动到外部存储器中实时计算。”

SEMPER X1闪存通过其LPDDR接口可提供高达3.2 GB/s的吞吐量。该公司表示,其多银行架构支持零停机的空中固件更新。重要的是,该设备符合ISO26262 ASIL-B标准,并提供高级纠错和其他安全功能。

xSPI无法跟上并且无法扩展

驱动LPDDR闪存需求的重要因素之一是,它正在取代xSPI,xSPI是一个现在不仅速度慢两个,而且无法扩展以满足未来需求的接口。Krishnegowda说:“如果你考虑一下今天的标准Octal SPI设备,它运行频率为200 MHz,使用LVCMOS I/O,你无法将其扩展到200 MHz以上。”。“所以,如果你想要更高的带宽,我必须采用新的内存标准。”

Krishnegowda表示,在考虑可用选项时,他们认为标准DRAM、HPM(HyperDRAM)或GDDR DRAM没有适合这些应用程序的性能。他说:“我们所需要的是与业界已经开发出的LPDDR4 DRAM相一致。”。

现在的xSPI NOR闪存速度太慢,无法扩展到200 MHz以上。同时,LPDDR4接口提供了从外部闪存设备直接执行代码所需的可扩展性和性能。(点击图片放大)

Krishnegowda说:“我们还选择了LPDDR4作为可扩展性,它实际上可以降到x8单通道设备,也可以降到有两个通道的通道a和通道B和x16。”。“这给了我们足够的可扩展性,可以将这一代产品提升到新的性能水平。”

同时,Krishnegowda指出,今天的标准Octal xSPI闪存设备不适合代码执行。他说:“你可以以非常低的频率执行代码,但当你使用千兆赫多核处理器时,你无法执行,因为你需要传输大量地址信息,才能尽快获得下一个数据。”。

不幸的是,无论您是在读还是在写,SPI都会让您提供一个命令。然后你必须以一种非常连续的方式重复一遍,这样你就不会流水线了。相比之下,LPDDR4协议允许您从数据中分离命令和地址。这样可以进行大量的流水线操作,减少延迟周期,并允许快速访问数据。

英飞凌表示,SEMPER X1目前正在进行采样,计划于2024年上市。

使用的所有图像均由Infineon提供