NVIDIA推出cuLitho:“计算光刻技术的突破”

本周,在NVIDIA的GTC上,该公司揭开了一套软件的帷幕,该软件可能会大幅提高现有光刻系统的分辨率。2023年3月22日作者:杰克·赫兹

随着半导体行业将芯片规模缩小,制造商面临着更大的生产挑战。

为了克服这些障碍,其中许多本质上是基础设施,生产设施现在严重依赖计算光刻,这是一种用于通过光刻提高分辨率的数学和算法方法。然而,随着节点尺寸远远缩小到22nm CMOS制造工艺之外,当前的计算光刻必须得到改进,以跟上重新铺设的吞吐量和能力问题。

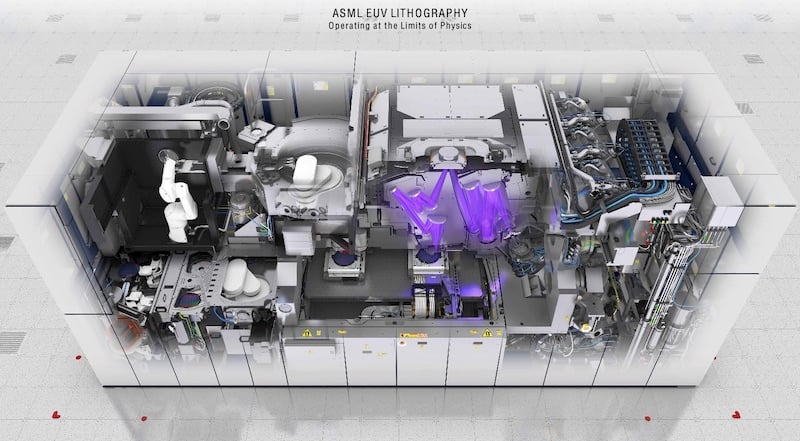

ASML EUV光刻机的渲染。图像由NVIDIA提供

昨天,在NVIDIA的GPU技术大会(GTC)上,该公司宣布了一个新的软件库,以加速计算光刻并解决这些挑战。

瑞利准则:光刻术的基础

在我们理解NVIDIA新软件的含义之前,我们必须首先讨论光刻的一些基本原理。

在半导体工业中,光刻是通过用光掩模覆盖衬底的区域并将特定波长的紫外光照射到暴露区域上来在半导体晶片上图案化芯片的过程。谈到光刻,可以说最重要的规范是关键尺寸,它定义了通过光刻工艺可以实现的最小特征尺寸。制造更小的半导体节点需要更小的临界尺寸。

可实现的临界尺寸由瑞利准则定义:

$$C_D=k_1\frac{\lambda}{NA}$$

哪里:

- k1.=取决于与芯片制造过程相关的许多因素的常数

- $$\lambda$$=使用的光的波长

- NA=光学器件的数值孔径,定义它们可以收集多少光

该标准描述了临界尺寸如何与光的曝光波长成比例,但也与投影光学器件的数值孔径成反比。常数k1.是表示光刻工艺中制造复杂性的集中参数,其物理极限为0.25。

计算光刻,一项急需改进的技术

从历史上看,随着半导体节点的缩小,光刻通过减少所用光的波长来降低临界尺寸。然而,就目前的行业而言,进一步降低波长需要全新的光刻技术,如极紫外(EUV)。

计算光刻。图片由ASML提供

虽然研究人员和制造商一直在努力实现更短的波长,但他们也在寻找减少k的方法1.因素要做到这一点,最强大和最重要的技术之一就是计算光刻。

计算光刻使用制造过程的算法模型来补偿制造缺陷。通过计算光刻,可以通过有意地使图案变形来优化光掩模,以考虑标准工艺中自然发生的物理和化学效应。通过这样做,计算光刻产生了更精确的光刻。在瑞利准则的背景下,这相当于降低了k1.值,从而增加临界尺寸。

NVIDIA使用cuLitho加速计算光刻

随着节点的缩小和设计变得更加复杂,算法建模的计算要求变得极其苛刻。为了解决这一限制,NVIDIA本周宣布了其用于计算光刻的新软件库。

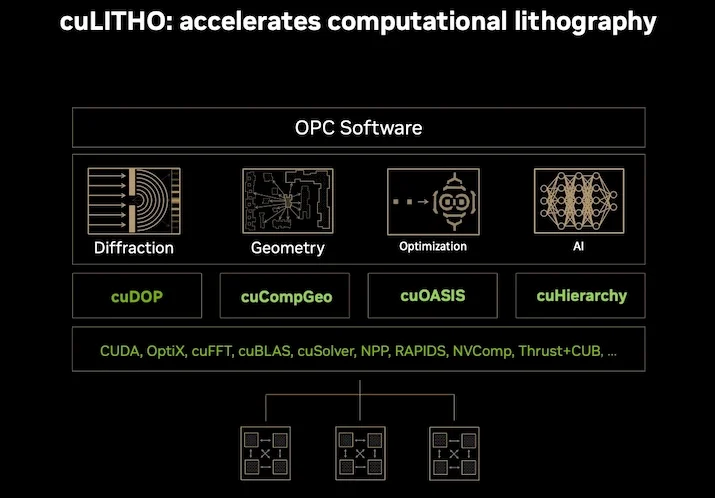

这个名为cuLitho的新库是NVIDIA CUDA库的扩展,该库针对与计算光刻相关的工作负载进行了优化。cuLitho由GPU加速的工具和算法组成,声称可以将半导体的制造过程比基于CPU的方法加快几个数量级。具体而言,NVIDIA声称cuLitho的反向光刻速度提高了40倍,导致每天生成的掩模比CPU系统多3到5倍。

cuLITHO是一个加速计算光刻的库,旨在嵌入OPC软件中。cuDOP用于衍射光学,cuCompGeo用于计算几何,cuOASIS用于优化,cuHierarchy用于人工智能。图像由NVIDIA提供

cuLitho的影响似乎很重要,导致半导体制造更快、更便宜、更准确,同时旨在保持摩尔定律的有效性。到目前为止,NVIDIA表示,ASML、台积电和新思科技已经采用了cuLitho,他们预计很快会有更多的大型晶圆厂效仿。