Bluespec与Synopsys合作进行RISC-V核心验证工作

通过他们的合作,两家公司希望能够为Bluespec的RISC-V核心实现更快、更好的功能验证测试。2023年1月24日作者:杰克·赫兹

随着RISC-V运动在行业中获得巨大的吸引力,许多工程师正在寻找令人兴奋的新方法来实现这项技术。其中,RISC-V在FPGA用户中变得特别受欢迎,允许软核处理器的简单和开放实现。

Bluespec是这一领域的一家公司,专门为Xilinx FPGA结构设计RISC-V处理器实现。现在,为了加强他们的努力,Bluespec与Synopsys合作,为他们技术的用户提供改进的设计验证工具。

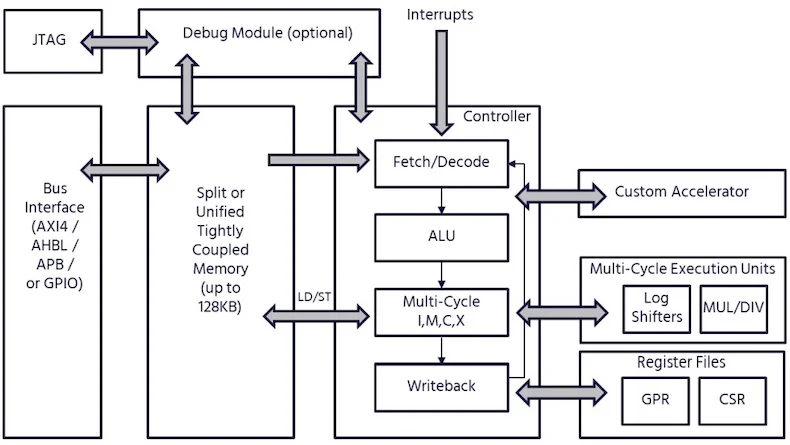

Bluespec的产品包括用于FPGA的RISC-V软核和专门用于Xilinx FPGA的RISC-V内核。图片由Bluespec提供

在本文中,我们将讨论RISC-V在FPGA世界中的流行,以及Bluespec和Synopsys之间的合作。

RISC-V和FPGA

随着RISC-V越来越受欢迎,它在FPGA爱好者中受到了极大的关注,这是有充分理由的。在许多方面,开发基于FPGA的处理器的最大好处是易于开发。尽管需要使用深奥的HDL进行编程,但FPGA是实现自定义硬件的一种简单得多的方式。

与FPGA相比,标准芯片开发需要设计者经历与制造物理芯片相关的整个生命周期,FPGA允许完全基于软件的处理器开发。

同样,RISC-V是一场植根于芯片设计民主化的运动。通过提供开源、免版税的指令集架构(ISA),RISC-V致力于为每个人和任何人提供芯片设计的访问权限。

有了这些共性,FPGA爱好者如此喜欢RISC-V的原因就很清楚了。在FPGA和RISC-V的交叉点上,存在着实现处理器核心的最简单、最直接的方法之一。理想情况下,这种合并会带来更大的设计灵活性、简单性,并减少新产品的上市时间。

Bluespec和Synopsys合作

Bluespec是一家大力参与RISC-V IP FPGA实现开发的公司。具体而言,该公司以其适用于Xilinx的RISC-V内核而闻名,这是一系列RISC-V处理器,专门为在Xilinx FPGA中实现而设计(Xilinx现在是AMD的一部分)。

Bluespec的通用RISC-V控制器(URC)框图。图片由Bluespec提供

上周,Bluespec宣布与Synopsys建立合作关系,以帮助推动Bluespec IP的设计和功能验证。具体而言,该合作伙伴关系将致力于为使用Bluespec RISC-V内核的RISC-V系统设计的验证和调试提供参考方法。在此范围内,合作伙伴关系将围绕新思科技的EDA流程和方法论的添加展开,以进一步支持Bluespec的特定IP。

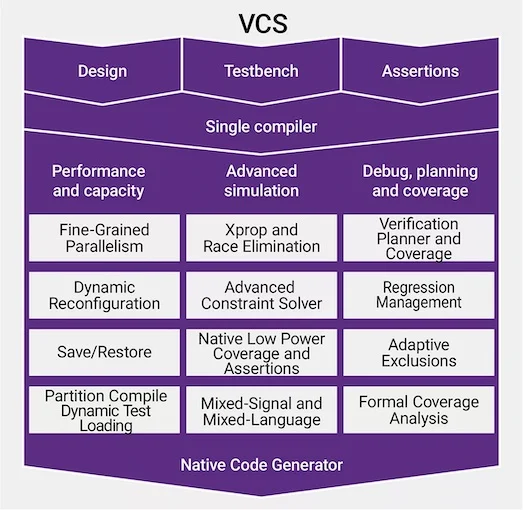

合作的目标是为RISC-V社区提供经验证的方法,以加快RISC-V处理器和系统的验证和调试。据两家公司介绍,合作的第一阶段将为新思的VCS功能验证解决方案和新思的Verdi调试系统提供参考方法和脚本。

Synopsys声称其VCS功能验证工具提供了最高性能的模拟和约束求解器引擎。图片由Synopsys提供

这两个Synopsys工具都符合通用验证方法(UVM)。此外,这些公司将致力于静态、正式、便携式刺激和FPGA合成的方法。

通过这次合作,两家公司希望帮助工程师改进RISC-V的设计,缩短上市时间。