计算机初创企业NeoLogic用“准CMOS”延长摩尔定律

在摩尔定律的死端附近工作,NeoLogic在新的超大规模集成电路设计中使用单晶体管逻辑来显著减少晶体管数量。2022年10月26日,杰克·赫兹

几十年来,摩尔定律推动了半导体行业的进步。然而,在过去10年里,包括NVIDIA首席执行官黄延森在内的一些行业领导者认为“摩尔定律已死”

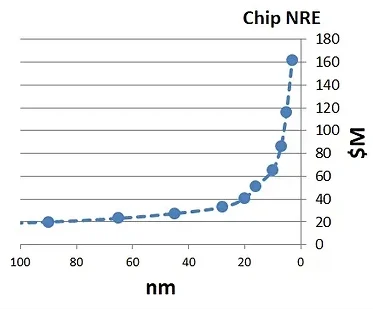

先进技术节点成本呈指数级增长的图表。图片由NeoLogic提供

现在,制造商和研究人员正在研究扩大半导体规模和提高性能的新方法。一家名为NeoLogic的初创公司正在采用一种独特的方法来应对这一挑战,即“超大规模集成电路设计的新范式”

晶体管缩放面临的挑战

摩尔定律依赖于制造业的努力,使晶体管栅极长度每一代下降0.7倍。减少晶体管栅极长度会带来许多重要好处:它降低了电路成本,降低了功耗,提高了性能,并增加了晶体管数量。

然而,随着扩展到5纳米及以下的领域,扩展可能会带来更多的问题,而不是解决问题。

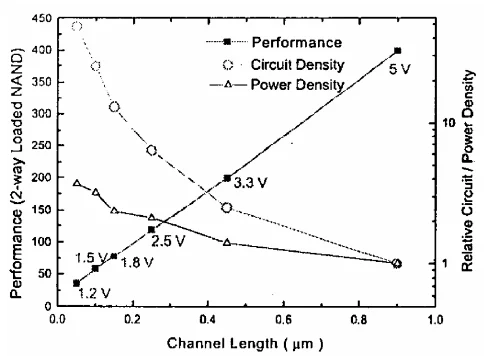

CMOS性能、功率密度和电路密度趋势。图片由美国国家航空航天局提供

其中一个问题是电路复杂性。随着越来越多的晶体管被添加到同一面积的芯片中,设计变得集群化和复杂,需要精心设计电源、时钟以及全局和本地信号的传输方案。最终,这种复杂性是一个限制因素,它限制了小型晶体管的规模和规模性能。

另一个挑战是功率密度。在更小的区域中有更多的晶体管,每个区域消耗的功率就会显著增加。这导致设计可靠性问题,因为高电路热。

NeoLogic设计“准CMOS”解决方案

为了应对这些挑战,初创公司NeoLogic设计了一个独特的解决方案。

NeoLogic由几位半导体和超大规模集成电路专家创立,完全放弃了CMOS设计。相反,NeoLogic使用其专利准CMOS技术设计超大规模集成电路IP,称为NeoMOS。

虽然NeoLogic没有透露其NeoMOS IP的许多细节,但该公司解释说,准CMOS架构将单晶体管逻辑(即nMOS或pMOS)与CMOS逻辑集成在一起,以创建逻辑门和电路。据该公司介绍,在超大规模集成电路设计中,增加单个晶体管逻辑会显著减少晶体管数量。

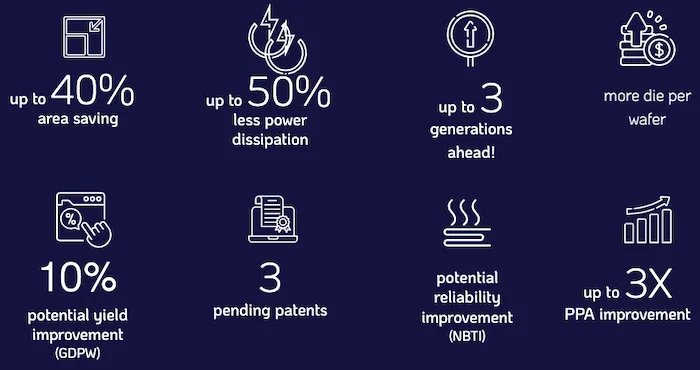

NeoLogic声称的NeoMOS的好处。图片由NeoLogic提供

NeoLogic声称,NeoMOS的好处包括降低成本、面积、功耗和设计复杂性。与标准CMOS产品相比,据说NeoMOS可以将功耗降低50%,面积减少40%,同时保持或改善电路延迟。NeoLogic表示,这相当于每瓦性能提高了3倍,使公司能够有效地跨越三代节点。

目前,NeoLogic通过许可协议出售其IP块,但有一天该公司希望出售自己的处理器和其他基于NeoMOS技术的技术。