敏捷模拟通过新的模拟IP加速物联网设计

Agile Analog的基础IP由基本的模拟构建块组成,无需定制内部设计即可实现更快的物联网设计。2022年10月24日,作者:Aaron Carman

总部位于剑桥的模拟IP公司Agile Analog最近完成了一组关键的模拟IP,以帮助物联网设计。尽管数字技术在物联网世界中占有重要地位,但模拟电路仍然是高性能芯片设计的主要要求。随着敏捷基础知识产权的发布,设计者可以在他们的设计中实现模拟构建块,以满足他们的需求并确保最佳性能。

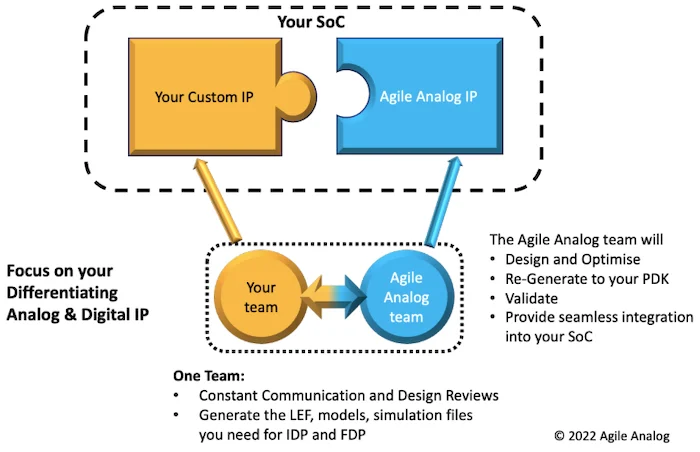

Agile Analog的预期用例:将Agile IP与自定义IP集成,以在不需要复杂的自定义模拟设计的情况下实现最佳解决方案。图片由Agile Analog提供

在本文中,我们将讨论Agile Analog的模拟IP方法及其基础IP的独特品质。此外,本文还将研究新发布的构建块在更大的物联网设计生态系统中的作用和影响。

这是一个数字世界;模拟只是生活在其中

数字电子对全球的影响不可估量。从求解微分方程到安全编码信息,数字电子在很大程度上负责我们所知道的日常计算。尽管如此,模拟电子是许多系统不可或缺的一部分。

即使是最简单的数字芯片也需要一些电源调节,以确保在电源轨上施加适当的电压。随着数字电路变得越来越复杂,需要更多的模拟功能,如低噪声放大器(LNA)、数据转换器、振荡器等等。

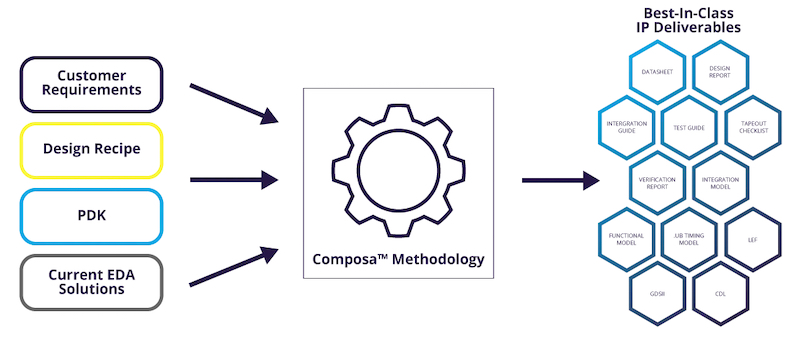

Composa方法论设计流程。在提供工艺信息、设计要求和当前解决方案后,Agile Analog可以生产高性能模拟电路。图片由Agile Analog提供

Agile Analog的目标很简单:为设计师提供改进的模拟电路,同时使ASIC或SoC的集成更容易。使用敏捷的Composa技术,设计者不再局限于可供他们选择的过程使用的IP。相反,Composa方法将选定的PDK作为开发所需模拟交付物的输入,使IP成为一个多流程解决方案。

为物联网设计奠定基础

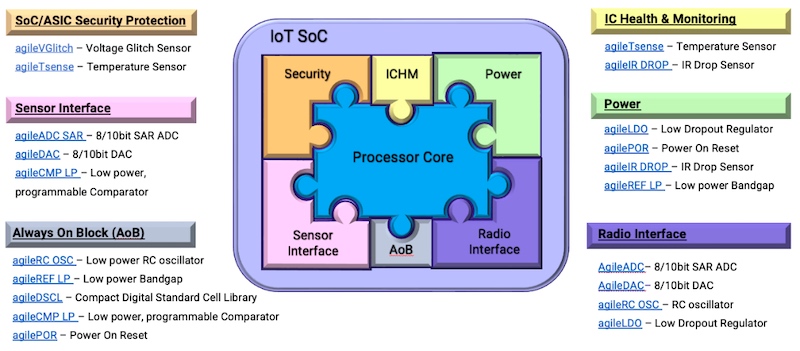

知道模拟设计并不是物联网设计师的重点,Agile analog已经着手通过其基础IP使模拟设计过程尽可能简单。基础知识产权由六个部分组成:

- SoC/ASIC保护

- 传感器接口

- 始终处于阻止状态

- IC健康监测

- 权力

- 无线电接口

使用这些块,设计者可以抽象模拟设计过程,并简单地使用构建块来实现所需的模拟功能。

Agile Analog的基础IP以及每个块的组件进行了进一步详细的解释。图片由Agile Analog提供

在确定流程节点后,Agile Analog的Foundation IP可以用于生成高性能模拟电路,而无需内部动手设计流程。这使物联网设计师能够专注于自己的创新,并使用敏捷的IP来填补模拟设计的空白。它还有助于满足带出截止日期,缩短上市时间,并生产出按设计工作的最终芯片,有助于节省总体成本。

数字系统中的模拟效率

与数字电子产品相比,敏捷的基础知识产权并不是模拟电子领域停滞不前的迹象,而是对相对复杂的设计过程的回应。模拟电子技术仍在进行创新,但并非所有设计师都需要这些创新。

那些需要已知模拟电路但不想经历设计过程的人可以很好地利用敏捷的IP,帮助加速物联网的发展,提高数字系统的模拟效率。