瑞萨利用STT-MRAM提高MCU的读写性能

瑞萨公司的一项新内存产品希望加快物联网应用程序的内存访问速度。2022年6月17日,杰克·赫兹

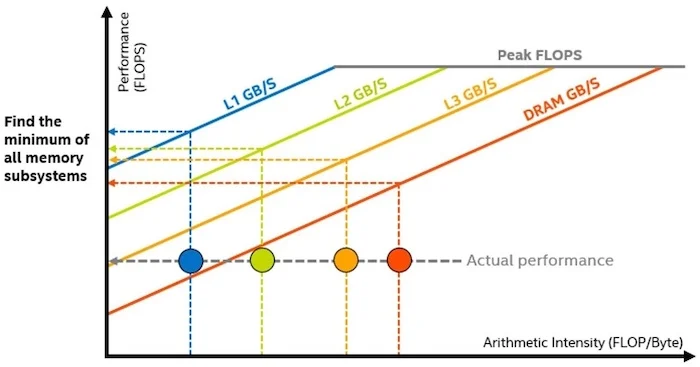

计算历史上的一个基本挑战是计算速度和内存访问之间的不匹配。在计算机体系结构层面上,这一挑战导致了更快的内存和缓存等概念的出现,以帮助缓解这些挑战。

物联网(IoT)设备面临的挑战是显而易见的,因为时钟频率和非易失性存储器访问读取频率之间的不匹配会导致空中传送(OTA)更新和通用计算等瓶颈。

内存瓶颈的示例。图片由英特尔提供

为了解决这一问题,公司正在寻找新形式的非易失性存储器作为解决方案,STT-MRAM是一个很有前途的候选者。

本周,瑞萨公司宣布了一项新的电路技术,可以在22纳米工艺上实现高速STT-MRAM。本文将介绍磁阻随机存取(MRAM)、STT-MRAM和瑞萨的最新公告。

MRAM背后的基础知识

关于非易失性存储器技术,许多人都称赞MRAM是下一个重要的东西。

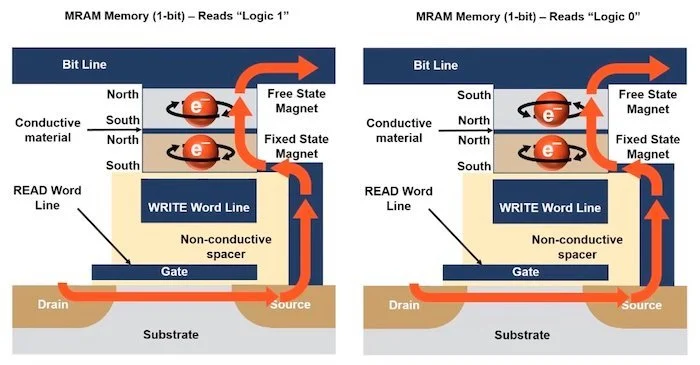

该技术利用了磁性材料的相对极性和电阻之间的关系。本质上,当两个磁体靠近放置时,它们的电阻会发生变化,这取决于它们的磁极相对于彼此的位置。

例如,如果一个磁体的北极与另一个的南极对齐,则结的电阻将较低,反之亦然。

同时处于逻辑1和0状态的MRAM单元。屏幕截图由Microchip提供[视频]

MRAM利用这种由磁体极性操纵的电阻变化,将其作为设备可以使用它在存储器中存储位的状态。电流可以影响每个磁体在给定方向上的极性,然后差分感测放大器可以读出产生的状态。

与其他形式的非易失性存储器相比,这种类型的存储器提供了几个关键优势,例如高存储器密度和低有源读/写电流。

什么是STT-MRAM?

在MRAM的世界中,存在许多不同的技术。其中,STT-MRAM是一种更有前景的技术。

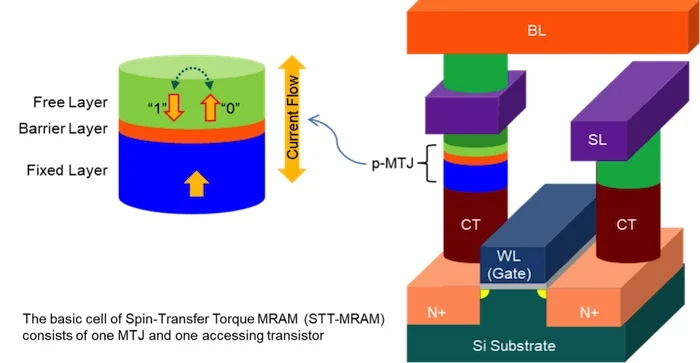

STT-MRAM是MRAM的一种变体,其中附近电子的自旋可以影响磁性隧道结(MTJ)的极性。在这种形式的MRAM中,电子自旋由穿过薄磁性层的极化电流操纵,将角动量转移到该层中,从而改变电子自旋。

STT-MRAM细胞。图片由Avalanche Technology提供

与其他形式的MRAM相比,STT-MRAM具有更低的功率和进一步扩展的能力。许多人认为,STT-MRAM有潜力成为领先的存储技术,因为它提供的性能与DRAM和SRAM相当,但可以扩展到10nm以下,这可能会挑战闪存的成本。

22 nm下更快的读/写操作

本周,瑞萨公司宣布开发了一种新的电路技术,该技术可以在22纳米节点的STT-MRAM中实现更快的读/写操作,成为头条新闻。

Renesas报告的主要创新是解决与MRAM的低不同感测电压相关的挑战,这些电压导致读/写速度慢和可靠性差,尤其是在高温下。

为了解决这个问题,瑞萨提出了一种新技术,该技术利用电容耦合来提高差分放大器输入端的电压。其结果是,即使在电流较低的情况下,也可以更快、更可靠地读取STT-MRAM状态。

Reneas测试芯片的平面布局。图片由瑞萨提供

Renesas声称,使用这项技术,写入操作的模式转换时间减少了30%,从而提高了写入操作的整体速度。

工程师们在一个基于22nm工艺的测试芯片上验证了这一点,该芯片包括一个32兆比特嵌入式MRAM存储单元阵列。据报道,测试芯片在150°C的最高温度下实现了5.9ns的随机读取访问时间和8.8MB/s的写入吞吐量。

对其他内存技术感兴趣吗?请继续阅读下面的文章。

新的RRAM阵列绕过1T1R限制,获得更好的非易失性存储器解决方案

瑞萨超越MRAM写入挑战,推动存储器技术向前发展

基于太空的闪存微芯片将闪存带到太空的利弊